The DCU can accept up to two load commands. If the data for the first load command is not

immediately available, the DCU can still accept the second load command. If the load data is not

required by subsequent instructions, those instructions will continue to execute.

If data is required

from either

load command, the CPU pipeline will stall until the load data has been delivered. The

pipeline will also stall until the second load has read the data array if a subsequent data cache

command is issued.

In general, if the fill buffer is being used and the next load or store command requires the fill buffer,

only one additional command can be accepted before causing additional DCU commands to stall the

pipeline.

The DCU can accept up to three outstanding store commands before stalling the CPU pipeline for

additional data cache commands.

The DCU can have two

flushes pending before stalling the CPU pipeline.

DCU cache operations other than loads and stores stall the CPU pipeline until all prior data cache

operations

complete. Any subsequent data cache command will stall the pipeline until the prior

operation is

complete.

The pipeline stalls when on-chip memory (OCM) asserts a hold signal. For loads or stores that are

held, the DCU can still accept one additional load or store command before stalling the pipeline for

subsequent commands.

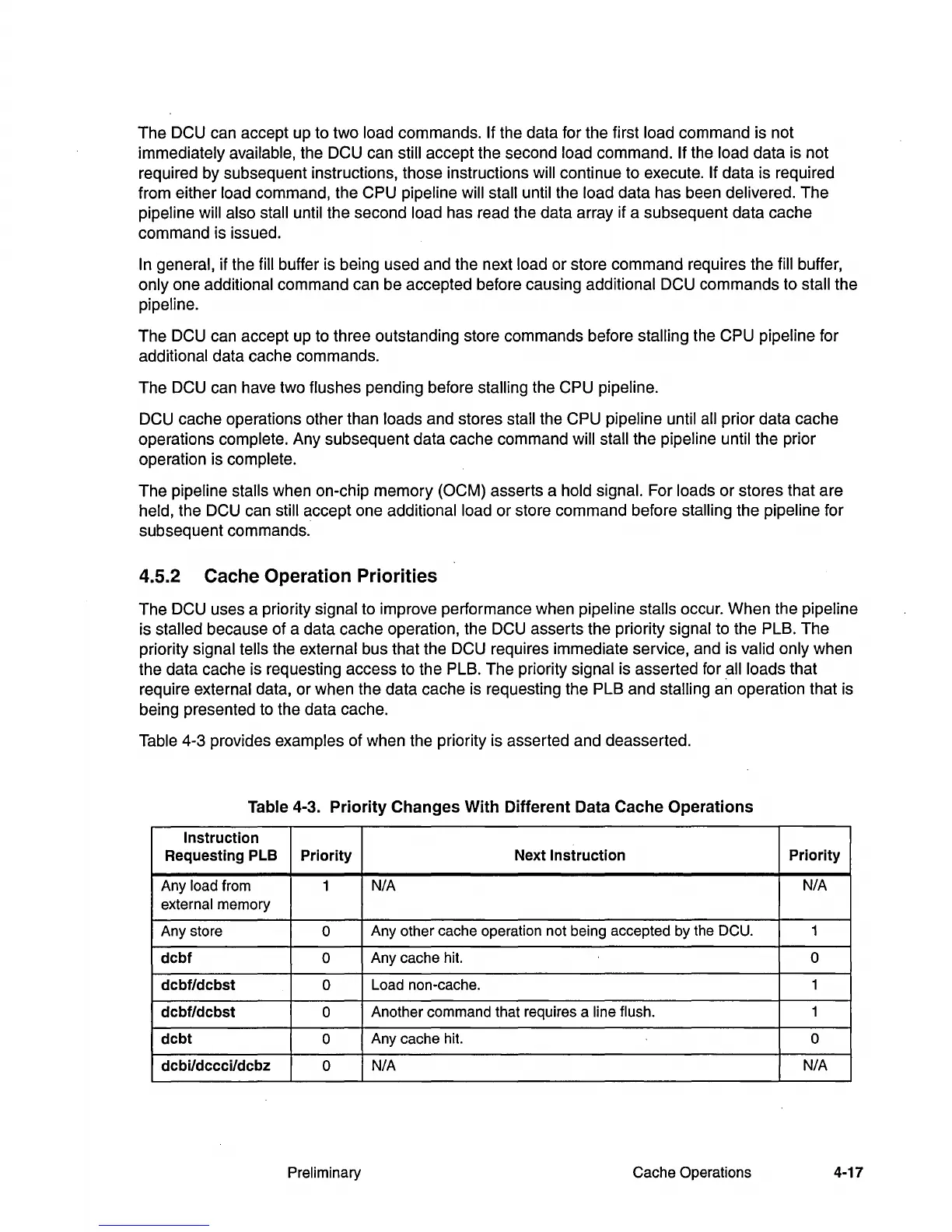

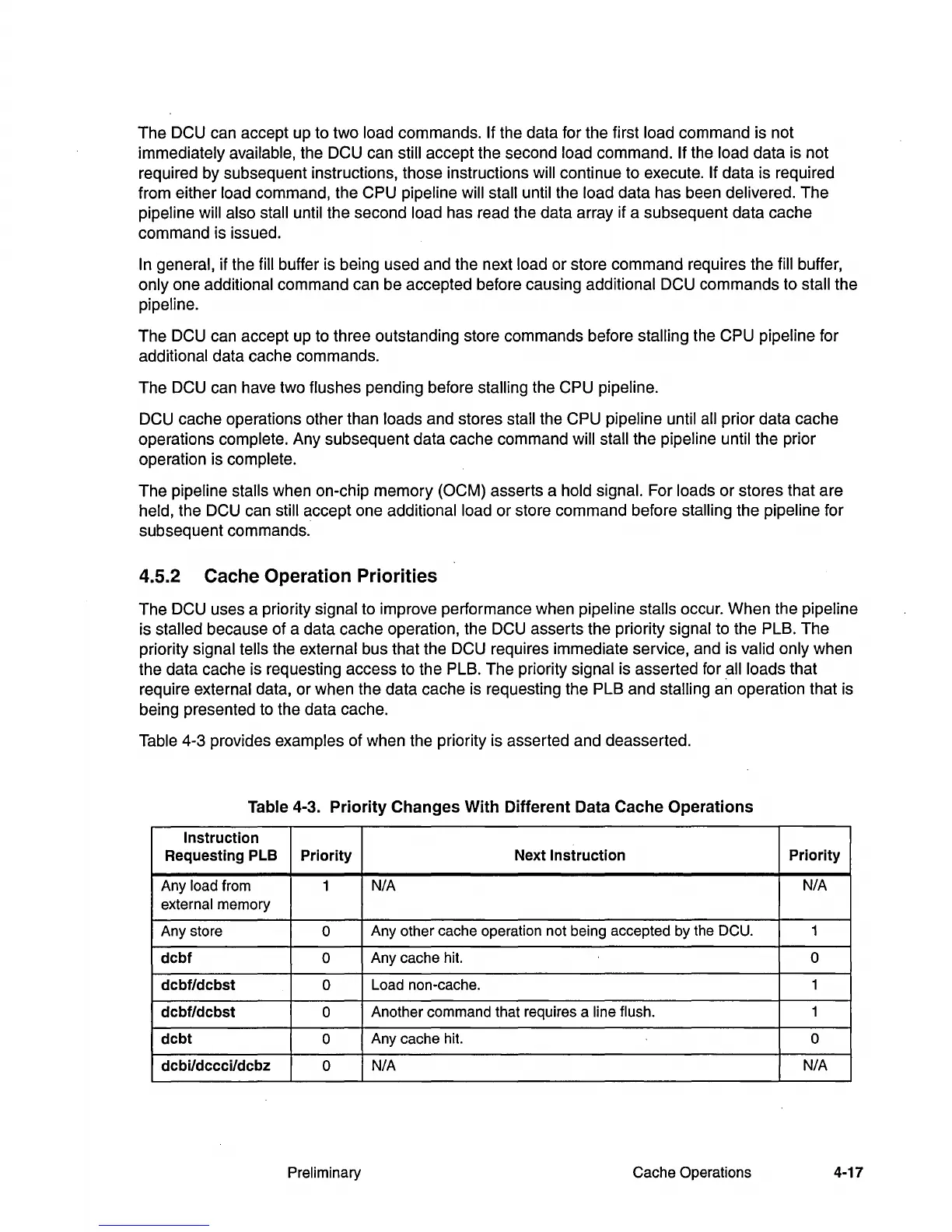

4.5.2 Cache Operation Priorities

The DCU uses a priority Signal to improve performance when pipeline stalls occur. When the pipeline

is stalled because of a data cache operation, the DCU asserts the priority signal to the PLB. The

priority

signal tells the external bus that the DCU requires immediate service, and is valid only when

the data cache is requesting access to the PLB. The priority signal is asserted for

~lIloads

that

require

external data, or when the data cache is requesting the PLB and stalling an operation that is

being presented to the data cache.

Table 4-3 provides examples of when the priority is asserted and deasserted.

Table 4-3. Priority Changes With Different Data Cache Operations

Instruction

Requesting PLB

Priority

Next

Instruction

Priority

Any load from 1

N/A

N/A

external memory

Any store

a

Any other cache operation not being accepted by the DCU. 1

dcbf

a

Any cache hit. a

dcbf/dcbst

a

Load non-cache.

1

dcbf/dcbst

a

Another command that requires a line flush.

1

dcbt

a

Any cache hit.

a

dcbi/dccci/dcbz

a

N/A

N/A

Preliminary

Cache Operations 4-17

Loading...

Loading...