16

UOF

Data storage

interrupt-UO

fault

o Excepting instruction did not cause a

UO

fault.

1 Excepting instruction did cause a

UO

fault.

17:31 Reserved

In

general, ESR bits are set to indicate the type of preCise interrupt that occurred; other bits are

cleared. However, the machine

check-instruction

(ESR[MCI]) bit behaves differently. Because

instruction-side machine checks can occur without an interrupt being taken (if

MSR[ME].= 0),

ESR[MCI]

can be set even while other ESR-setting interrupts (program, data storage, DTLB-miss)

occurring. Thus, data storage and program interrupts leave

ESR[MCI] unchanged, clear all other ESR

bits, and set the bits associated with any data storage or program interrupts occurred. Enabled

instruction-side machine checks

(MSR[ME] =

1)

set ESR[MCI] and clear the data storage and

program interrupt bits.

If a machine

check-instruction

interrupt occurs but is disabled (MSR[ME] = 0), it sets ESR[MCI] but

leaves the data storage and program interrupt bits alone.

If a machine

check-instruction

interrupt

occurs while

MSR[ME] =

0,

and

the instruction upon which the machine

check-instruction

interrupt

is occurring also is some other kind of ESR-setting instruction (program, data storage, DTLB-miss, or

instruction storage interrupt),

ESR[MCI] is set to indicate that a machine

check-instruction

interrupt

occurred; the other

ESR bits are set or cleared to indicate the other interrupt. These scenarios are

summarized

in

Table 10-5

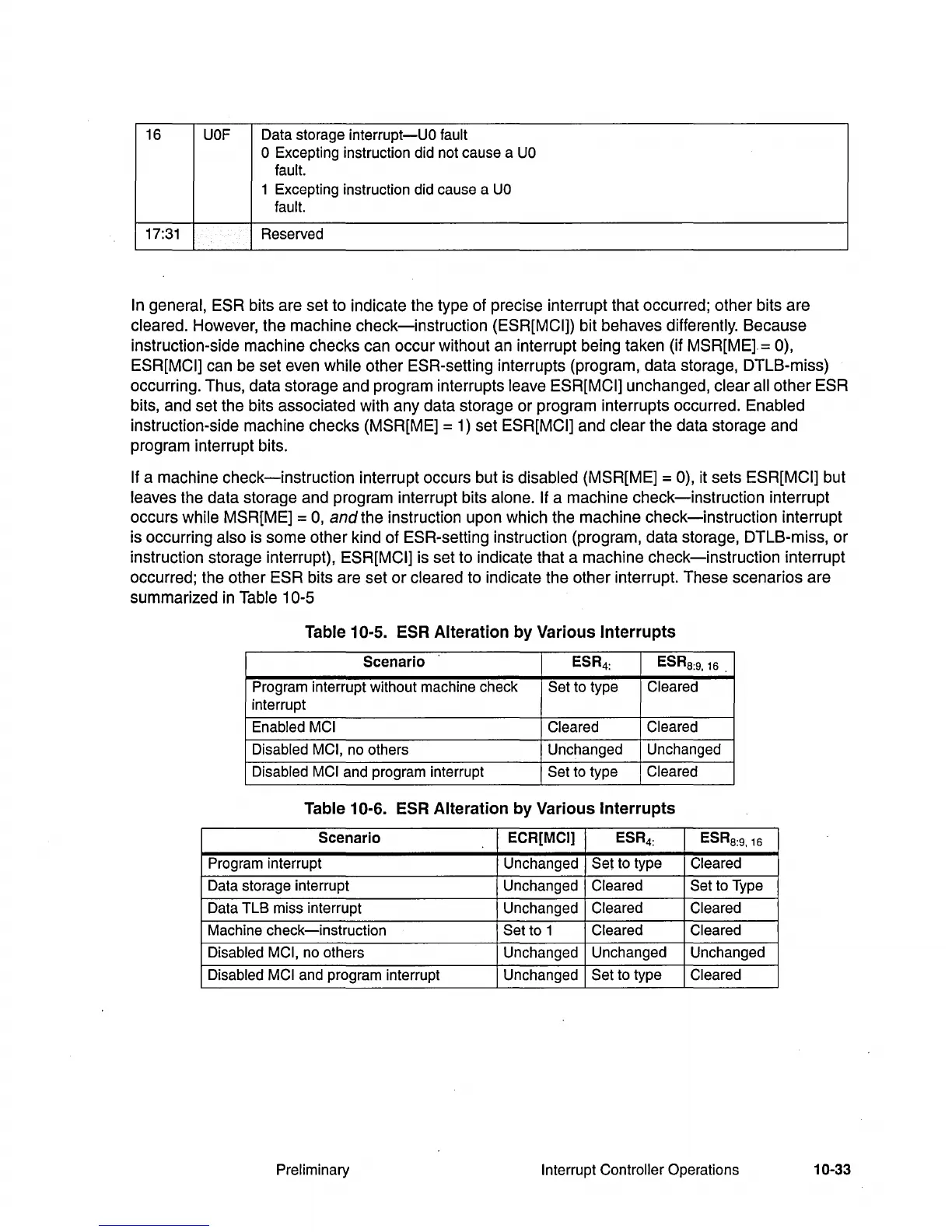

Table 10-5.

ESR

Alteration by Various Interrupts

Scenario

ESR

4

:

ESR

s

:

9

,

16 .

Program interrupt without machine check Set to type Cleared

interrupt

Enabled MCI Cleared

Cleared

Disabled MCI,

no others Unchanged

Unchanged

Disabled MCI and program interrupt Set to type Cleared

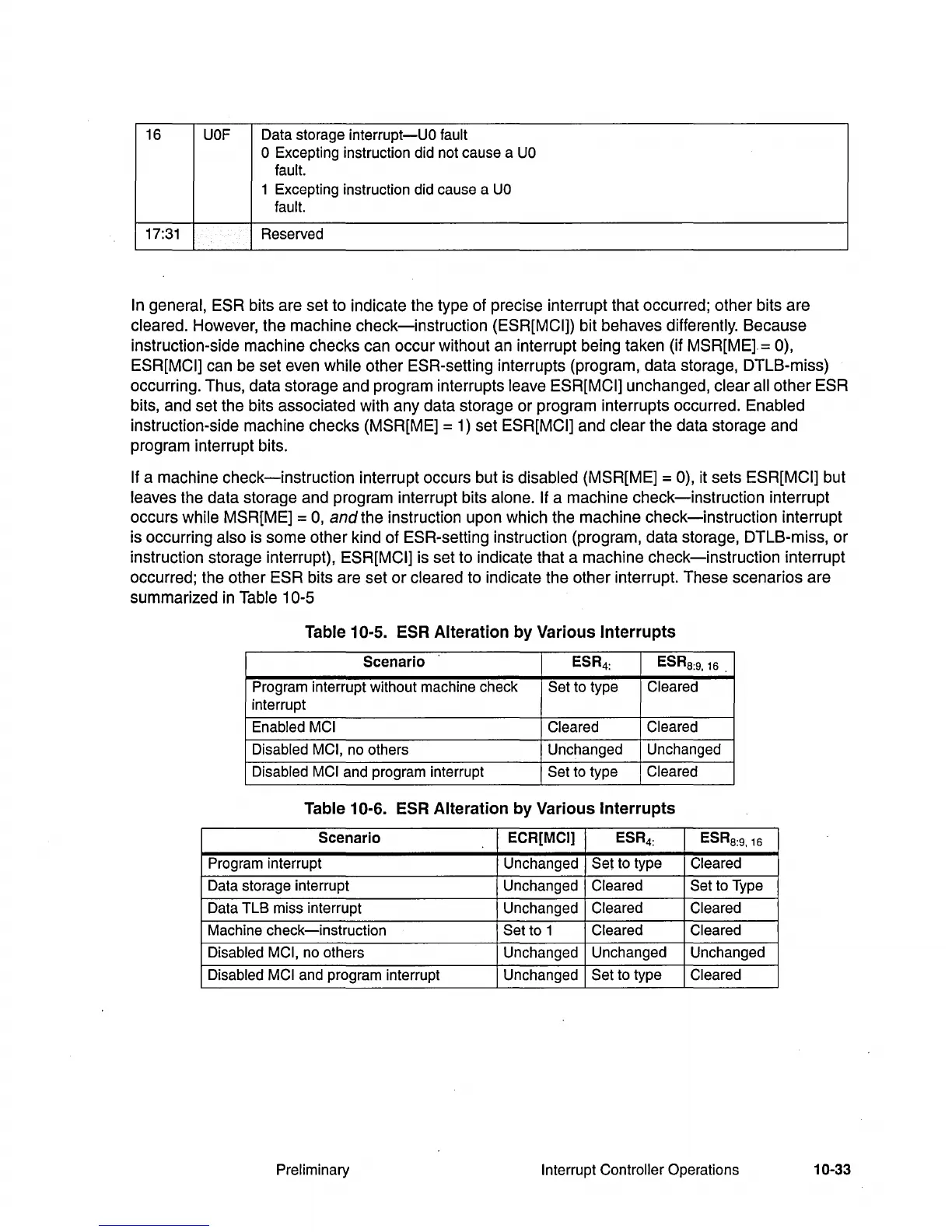

Table 10-6.

ESR

Alteration by Various Interrupts

Scenario

ECR[MCI]

ESR

4

:

ESR

s

:

9

,16

Program interrupt Unchanged Set to type Cleared

Data storage interrupt Unchanged Cleared Set to Type

Data TLB miss interrupt Unchanged

Cleared Cleared

Machine

check-instruction

Set to 1 Cleared Cleared

Disabled MCI,

no others Unchanged Unchanged Unchanged

Disabled MCI and program interrupt Unchanged Set to type Cleared

Preliminary Interrupt Controller

Operations

10-33

Loading...

Loading...