31

EIR6P ExternallRO 6 Polarity

o An externallRO 6 interrupt has negative polarity.

1 An externallRO 6 interrupt has positive polarity.

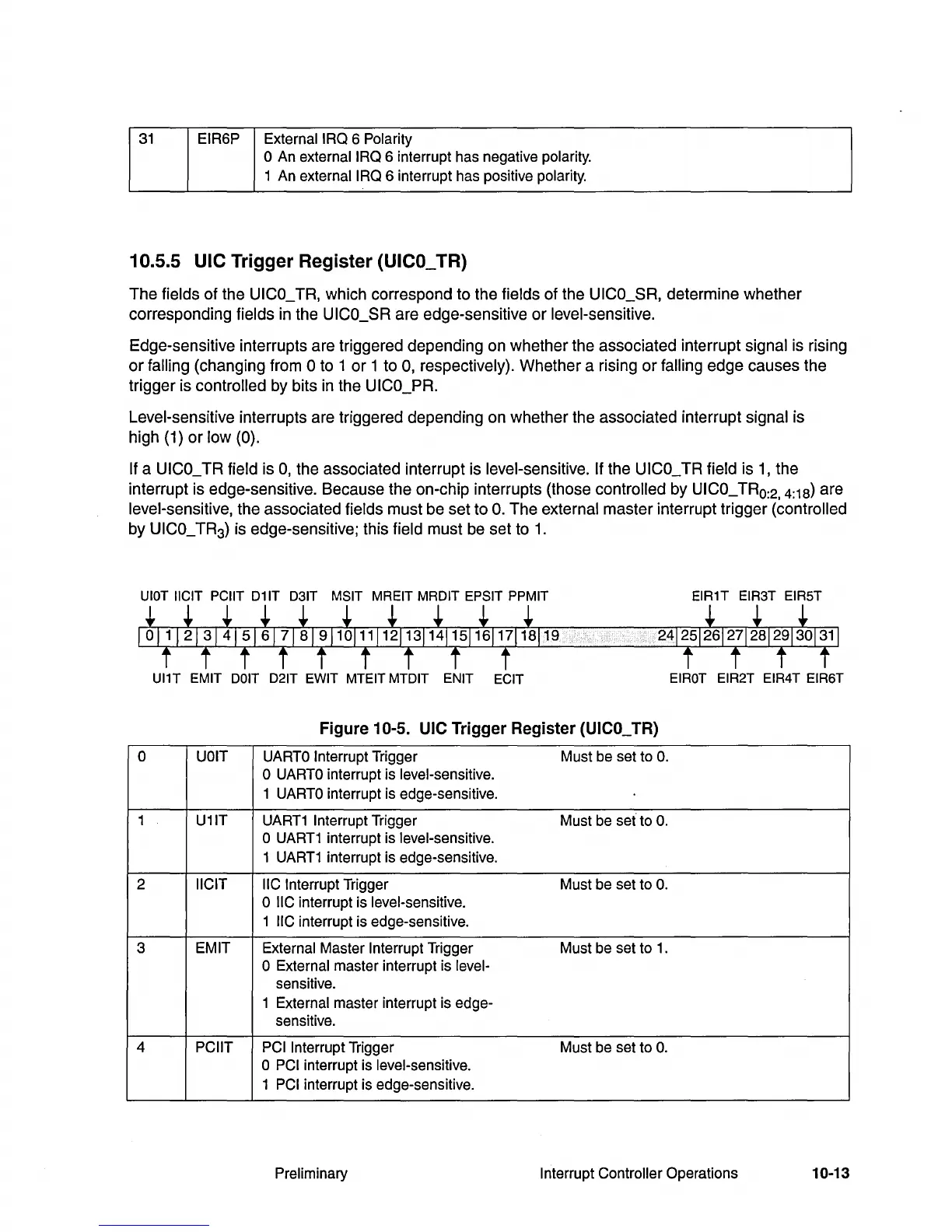

10.5.5 UIC Trigger Register

(UICO_

TR)

The fields of the UICO_ TR, which correspond to the fields of the UICO_SR, determine whether

corresponding

fields

in

the UICO_SR are edge-sensitive or level-sensitive.

Edge-sensitive interrupts are triggered depending on whether the associated interrupt

signal is rising

or

falling (changing from ° to 1 or 1 to

0,

respectively). Whether a rising

or

falling edge causes the

trigger is

controlled by bits

in

the UICO_PR.

Level-sensitive interrupts are triggered depending on whether the associated interrupt signal is

high (1)

or

low (0).

If

a UICO_ TR field is

0,

the associated interrupt is level-sensitive. If the UICO_ TR field is

1,

the

interrupt is edge-sensitive. Because the on-chip interrupts (those

controlled by UICO_ TR

o

:

2

•

4:18) are

level-sensitive, the associated fields must be set to

0.

The external master interrupt trigger (controlled

by UICO_ TR

3

)

is edge-sensitive; this field must be set to

1.

UIOT

liCIT PCIIT

D11T

D31T

MSIT MREIT MRDIT EPSIT PPMIT

EIRn

EIR3T EIR5T

uln

EMIT

DOlT

D21T

EWIT MTEIT MTDIT ENIT ECIT

EIROT

EIR2T EIR4T EIR6T

Figure

10-5. UIC

Trigger

Register

(UICO_ TR)

0

UOIT

UARTO

Interrupt Trigger Must be set to

o.

o

UARTO

interrupt is level-sensitive.

1

UARTO

interrupt is edge-sensitive.

1

U11T

UART1

Interrupt Trigger

Must be set to

O.

o

UART1

interrupt is level-sensitive.

1

UART1

interrupt is edge-sensitive.

2 liCIT IIC Interrupt Trigger Must be set to

o.

o IIC interrupt is level-sensitive.

1

IIC interrupt is edge-sensitive.

3

EMIT External Master Interrupt Trigger Must be set to

1.

o External master interrupt is level-

sensitive.

1 External master interrupt is edge-

sensitive.

4 PCIIT PCI Interrupt Trigger Must be set to

O.

o PCI interrupt is level-sensitive.

1

PCI interrupt is edge-sensitive.

Preliminary

Interrupt

Controller Operations 10-13

Loading...

Loading...