12:13

EMS External Master Size

Width of the attached external master.

008-bit

01

16-bit

1032-bit

11

No external master attached

14

PME Power Management Enable

o Disabled

1 Enabled

15:19 PMT Power Management Timer

The EBC makes a sleep request to the Clock

0-31

and Power Management unit when PME=1

and the EBC has been idle for 32*PMT

PerClk cycles.

20:31

Reserved

16.6.2 Peripheral Bank Configuration Registers (EBCO_BnCR)

These registers must be configured to enable memory

in

each respective bank. Boot ROM must be

attached to bank

0 if installed.

If a boot ROM is present, the bank 0 starting address register is loaded with a value of OxFFE, and

the bank

0 size register is loaded with a value of

Ob001

(2MB) immediately following SysReset

inactive.

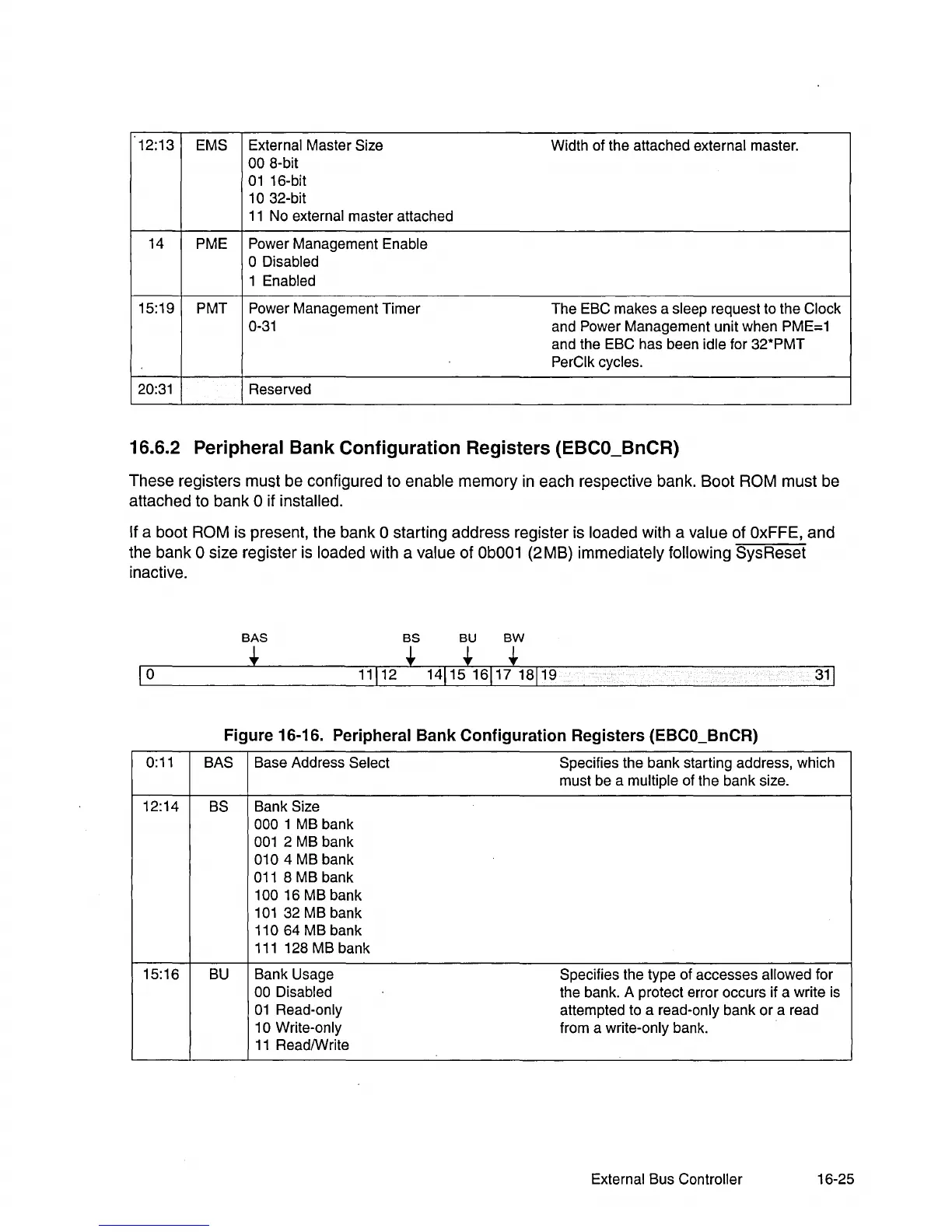

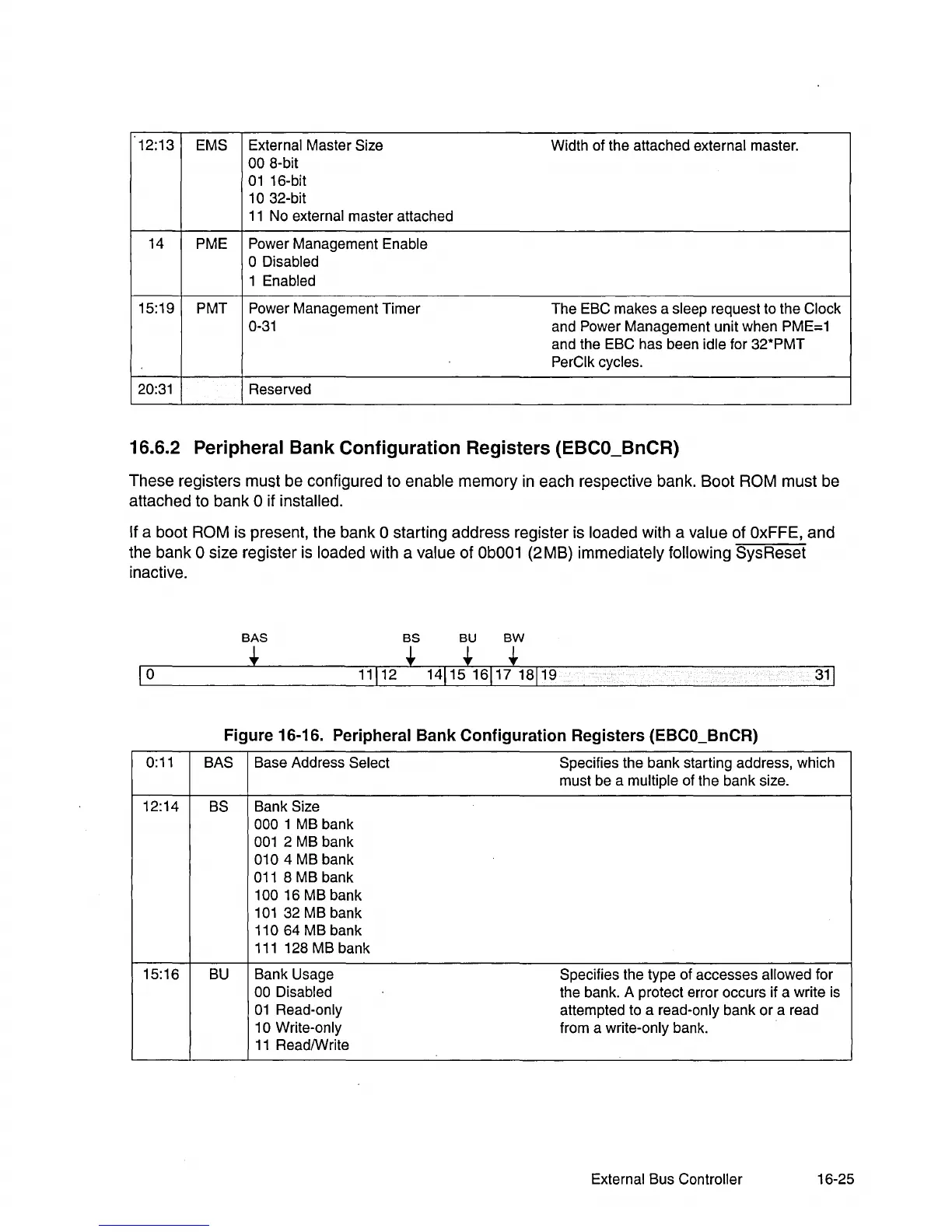

BAS

BS

BU

BW

1

0

•

11112

141151611718119

• t t

311

Figure 16-16. Peripheral Bank Configuration Registers (EBCO_BnCR)

0:11

BAS Base Address Select

Specifies the bank starting address, which

must be a multiple of the bank size.

12:14

BS Bank Size

000

1 MB bank

001

2 MB bank

0104

MB bank

011

8 MB bank

100 16 MB bank

101

32 MB bank

11064

MB bank

111

128 MB bank

15:16

BU

Bank Usage

Specifies the type of accesses allowed for

00 Disabled the bank. A protect error occurs if a write is

01

Read-only

attempted to a read-only bank or a read

10 Write-only

from a write-only bank.

11

Read/Write

External Bus Controller 16-25

Loading...

Loading...