16.4.1 Device-Paced Single Read Transfer

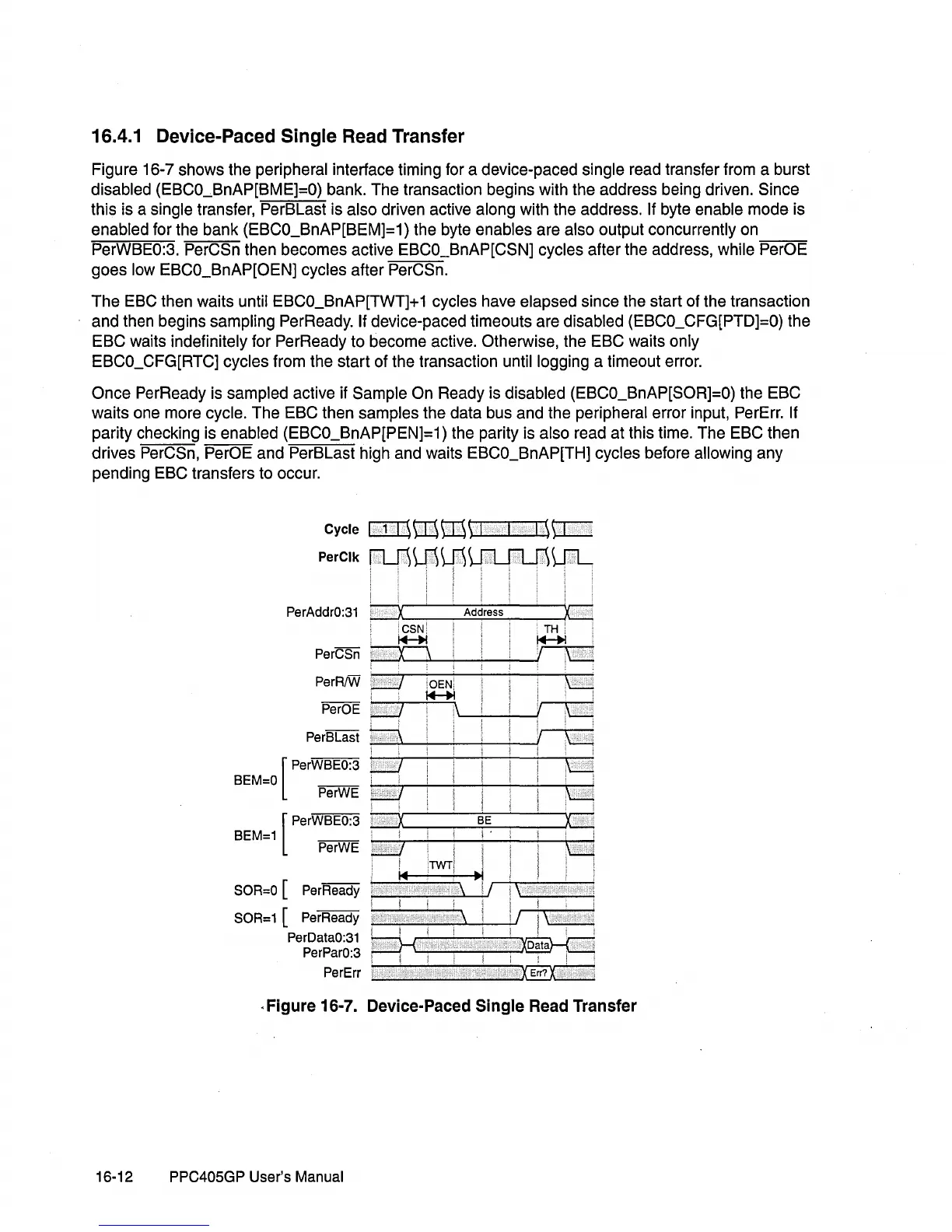

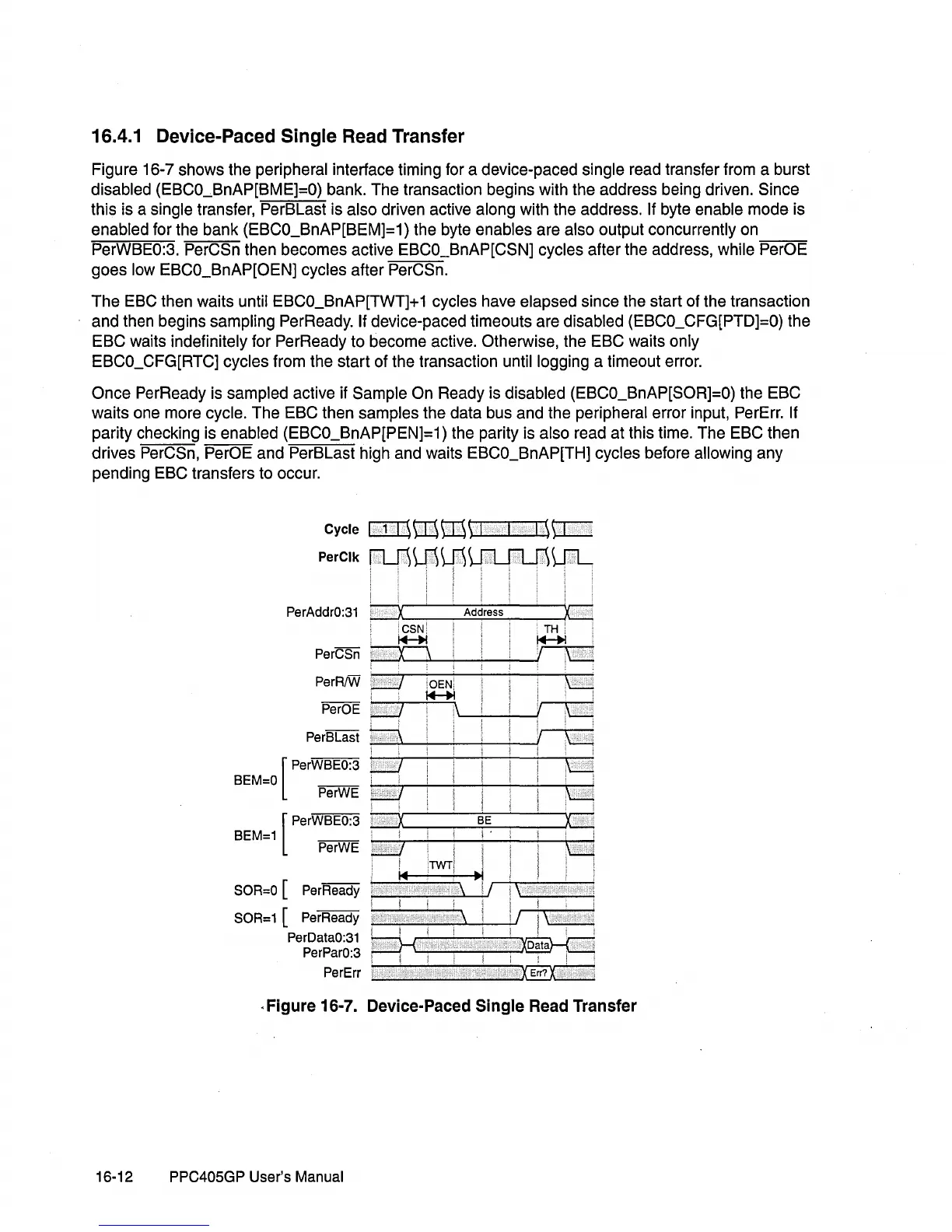

Figure 16-7 shows the peripheral interface timing for a device-paced single read transfer from a burst

disabled (EBCO--,BnAP[BME]=O) bank. The transaction begins with the address being driven. Since

this is a

single transfer, PerBLast is also driven active along with the address. If byte enable mode is

enabled for the bank (EBCO_BnAP[BEM]=1) the byte enables are also output concurrently on

PerWBEO:3. PerCSn then becomes active EBCO_BnAP[CSN]

cycles after the address, while PerOE

goes low EBCO_BnAP[OEN] cycles after PerCSn.

The EBC then waits until EBCO_BnAP[TWT]+1

cycles have elapsed since the start of the transaction

and then begins

sampling PerReady.

If

device-paced timeouts are disabled (EBCO_CFG[PTD]=O) the

EBC waits

indefinitely for PerReady to become active. Otherwise, the EBC waits only

EBCO_CFG[RTC] cycles from the start of the transaction until logging a timeout error.

Once PerReady is sampled active if Sample On Ready is disabled (EBCO_BnAP[SOR]=O) the EBC

waits one more

cycle. The EBC then samples the data bus and the peripheral error input, PerErr. If

parity checking is enabled (EBCO_BnAP[PEN]=1) the parity is also read at this time. The EBC then

drives PerCSn,

PerOE and PerBLast high and waits EBCO_BnAP[TH] cycles before allowing any

pending EBC transfers to occur.

Cycle

c:I:O

OJ

OJ

~

1

I)

tc=

PerClk

ru)W~~LrL

PerAddrO:31

::::::J

Address C

iCSN

TH

~,i,

~

PerCSn~

PerRiW

C2..J

DEN L

~

PerOE

0 \I-----:------(\2i

PerBLast

'-C3;....

..

;.....L....-.........

'-'-----'--..:...---1r-o

[

PerWBEO:3

3

..

'

.....

' C

BEM=O

;,....;

~;r-+-~~-~~~~

PerWE

9 G

BEM=1

[per::~;~

~

!

~E

§

TWTI

I

SOR=O

[ PerReady

SOR=1

[ PerReady

PerDataO:31

PerParO:3

~~I"!::::==±:\~~l/r--:-1

T""\

-~---:'

---"~~~\

II

:c::J

I I ! ! ;

~~----'-'-'-'-'-~~

PerErr

~

<Figure 16-7. Device-Paced Single Read Transfer

16-12 PPC405GP User's Manual

Loading...

Loading...