contents of the EVPR and the low-order 16 bits of the program counter are written with Ox1000.

Interrupt

processing begins at the address

in

the program counter.

To

clear a PIT interrupt, the interrupt handling routine must clear the PIT interrupt bit, TSR[PIS].

Clearing

is performed by writing a word to TSR, using an

mtspr

instruction, that has 1

in

bit positions

to be

cleared and 0

in

all other bit positions. The data written to the TSR is not direct data, but a mask;

a 1

clears the bit and 0 has no effect.

Executing an rfi instruction restores the program counter from

SRRO

and the MSR from

SRR1

, and

execution resumes at the address

in

the program counter.

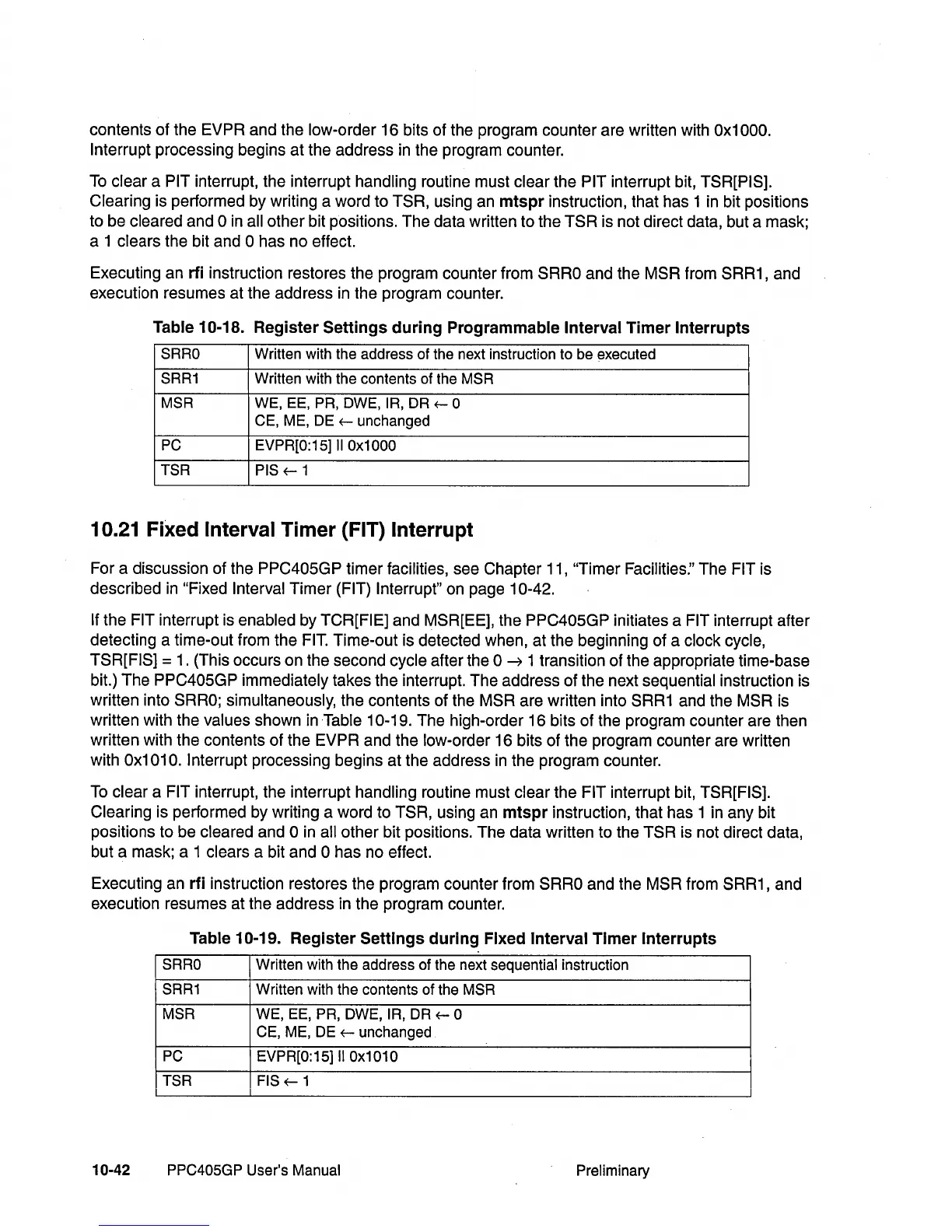

Table

10-18.

Register

Settings

during

Programmable

Interval

Timer

Interrupts

SRRO

Written with the address of the next instruction to be executed

SRR1

Written with the contents of the MSR

MSR

WE, EE, PR, OWE, IR, DR

~

0

CE, ME, DE

~

unchanged

PC

EVPR[O:15]II Ox1000

TSR

PIS~

1

10.21 Fixed Interval Timer (FIT) Interrupt

For a discussion of the PPC405GP timer facilities, see Chapter 11, "Timer Facilities:' The FIT is

described

in

"Fixed Interval Timer (FIT) Interrupt" on page 10-42.

If

the FIT interrupt is enabled by TCR[FIE] and MSR[EE], the PPC405GP initiates a FIT interrupt after

detecting a time-out from the

FIT.

Time-out is detected when, at the beginning of a clock cycle,

TSR[FIS]

=

1.

(This occurs on the second cycle after the 0

~

1 transition of the appropriate time-base

bit.) The

PPC405GP immediately takes the interrupt. The address of the next sequential instruction is

written into

SRRO;

simultaneously, the contents of the MSR are written into SRR1 and the MSR

is

written with the values shown

in

Table 10-19. The high-order 16 bits of the program counter are then

written with the contents of the EVPR and the

low-order 16 bits of the program counter are written

with

Ox1

01

O.

Interrupt processing begins at the address

in

the program counter.

To

clear a FIT interrupt, the interrupt handling routine must clear the FIT interrupt bit, TSR[FIS].

Clearing

is performed by writing a word to TSR, using an

mtspr

instruction, that has 1 in any bit

positions to be

cleared and 0

in

all other bit positions. The data written to the TSR is not direct data,

but a mask; a 1

clears a bit and 0 has no effect.

Executing an rfi instruction restores the program counter from

SRRO

and the MSR from SRR1, and

execution resumes at the address in the program counter.

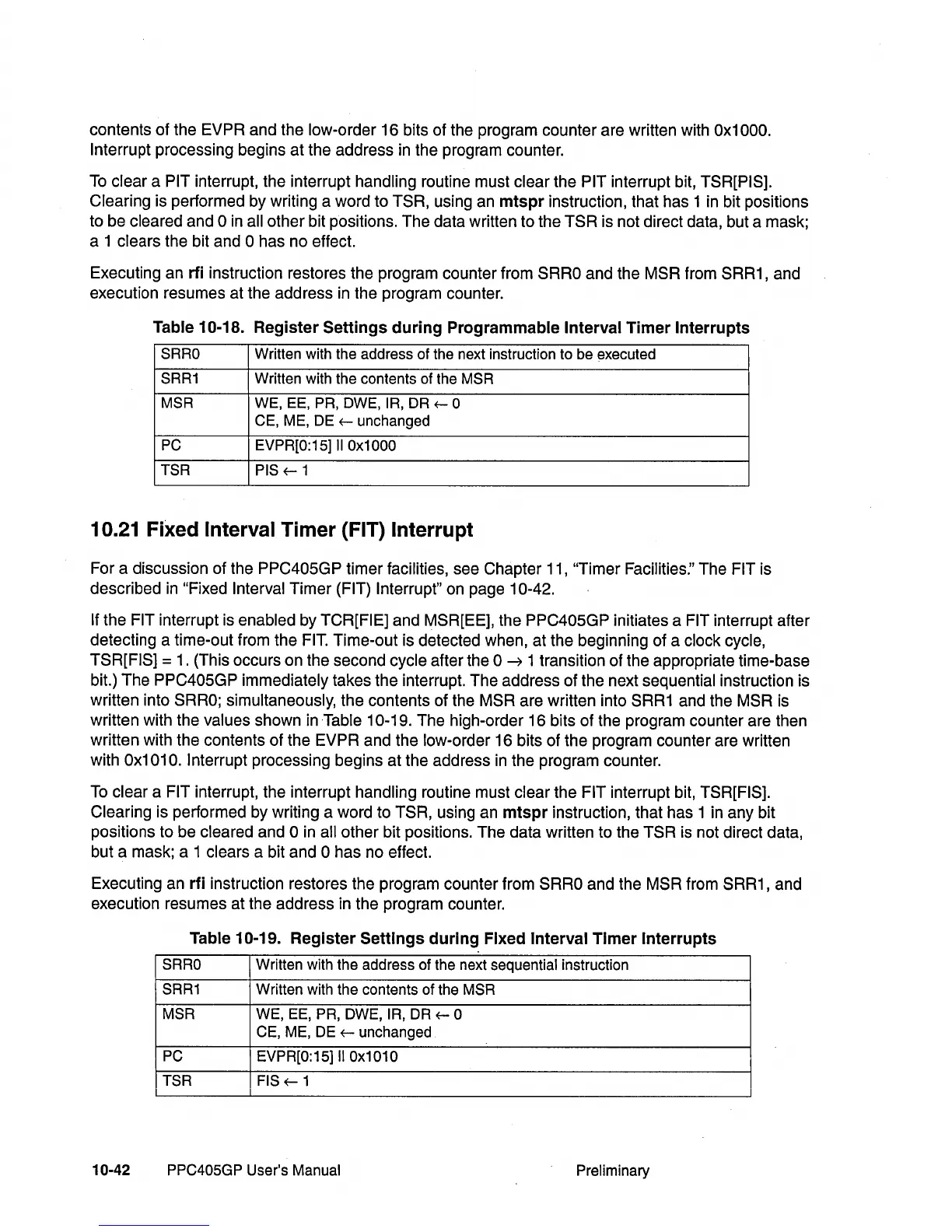

Table

10-19.

Register

Settings

during

Fixed

Interval

Timer

Interrupts

SRRO

Written with the address of the next sequential instruction

SRR1

Written with the contents of the MSR

MSR

WE, EE, PR, OWE, IR, DR

~

0

CE, ME, DE

~

unchanged

PC

EVPR[O:15]II Ox1010

TSR

FIS~

1

10-42

PPC405GP User's Manual

Preliminary

Loading...

Loading...