• The IPG counter, which controls transmit deferral during the IPG between

back-to~back

transmits,

is started when transmit activity for the first packet ends, instead of when transmit and carrier

activity end. '

• SQE test is not performed.

• Collision indication is ignored.

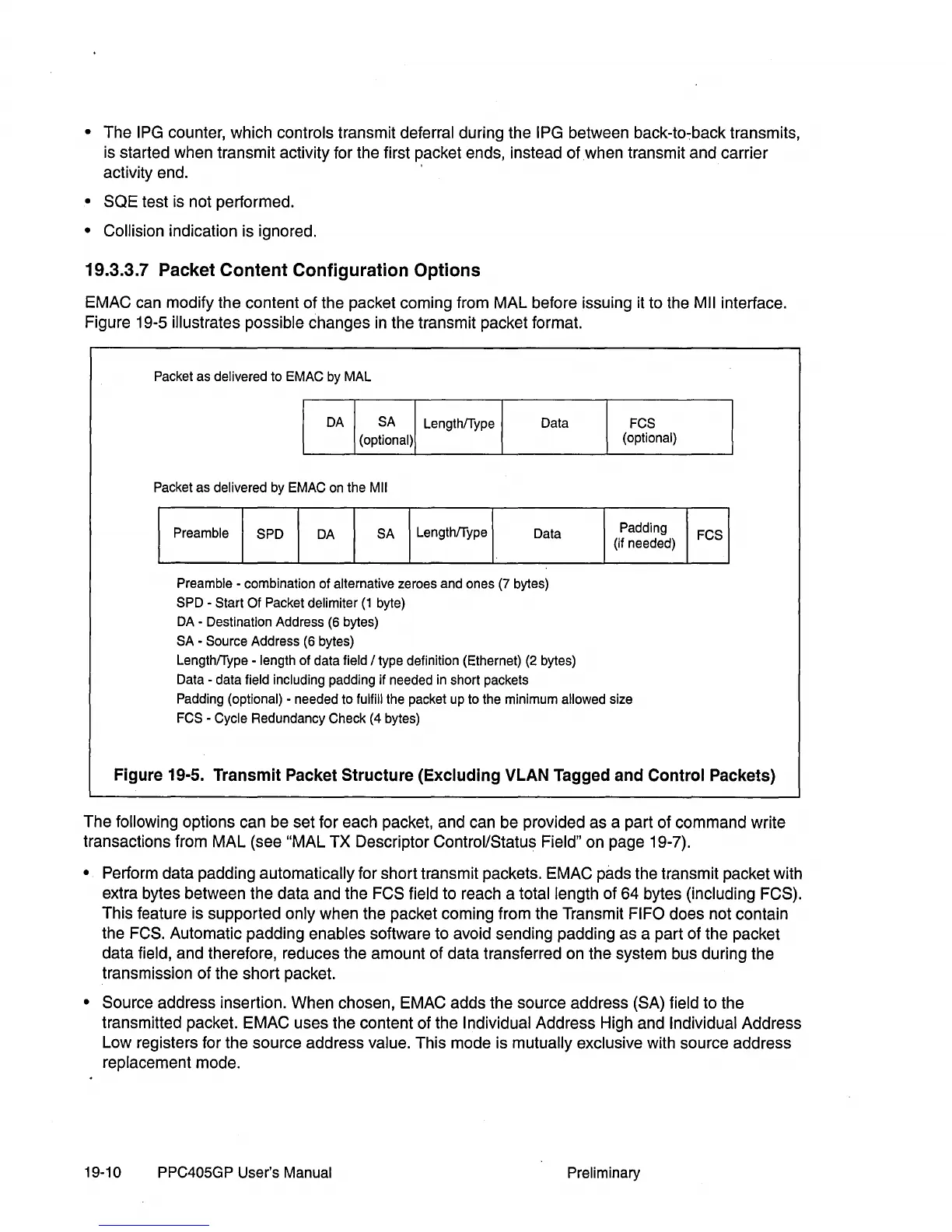

19.3.3.7 Packet Content Configuration Options

EMAC can modify the content of the packet coming from MAL before issuing it to the Mil interface.

Figure 19-5

illustrates possible changes

in

the transmit packet format.

Packet

as

delivered

to

EMAC

by

MAL

DA

SA

LengthfType

Data

(optional)

Packet

as

delivered

by

EMAC

on

the

Mil

Preamble

SPD

DA

SA

LengthfType

Data

Preamble

- combination

of

alternative

zeroes

and

ones

(7

bytes)

SPD

- Start

Of

Packet

delimiter

(1

byte)

DA

- Destination Address

(6

bytes)

SA

-

Source

Address

(6

bytes)

LengthfType

- length of data field /

type

definition (Ethernet)

(2

bytes)

Data

- data field including

padding

if

needed

in

short

packets

FCS

(optional)

Padding

(if

needed)

Padding

(optional) -

needed

to

fulfill

the

packet

up

to

the

minimum

allowed

size

FCS

-

Cycle

Redundancy

Check

(4

bytes)

FCS

Figure 19·5. Transmit Packet Structure (Excluding VLAN Tagged and Control Packets)

The following options can be set for each packet, and can be provided as a part of command write

transactions from MAL (see

"MAL

TX

Descriptor Control/Status Field" on page 19-7).

• Perform data padding automatically for short transmit packets. EMAC pads the transmit packet with

extra bytes between the data and the

FCS field to reach a total length of 64 bytes (including FCS).

This feature is supported only when the packet coming from the Transmit FIFO does not contain

the

FCS. Automatic padding enables software to avoid sending padding as a part of the packet

data

field, and therefore, reduces the amount of data transferred on the system bus during the

transmission of the short packet.

• Source address insertion. When chosen, EMAC adds the source address (SA) field to the

transmitted packet. EMAC uses the content of the

Individual Address High and Individual Address

Low registers for the source address

value. This mode is mutually exclusive with source address

replacement mode.

19-10 PPC405GP User's Manual

Preliminary

Loading...

Loading...