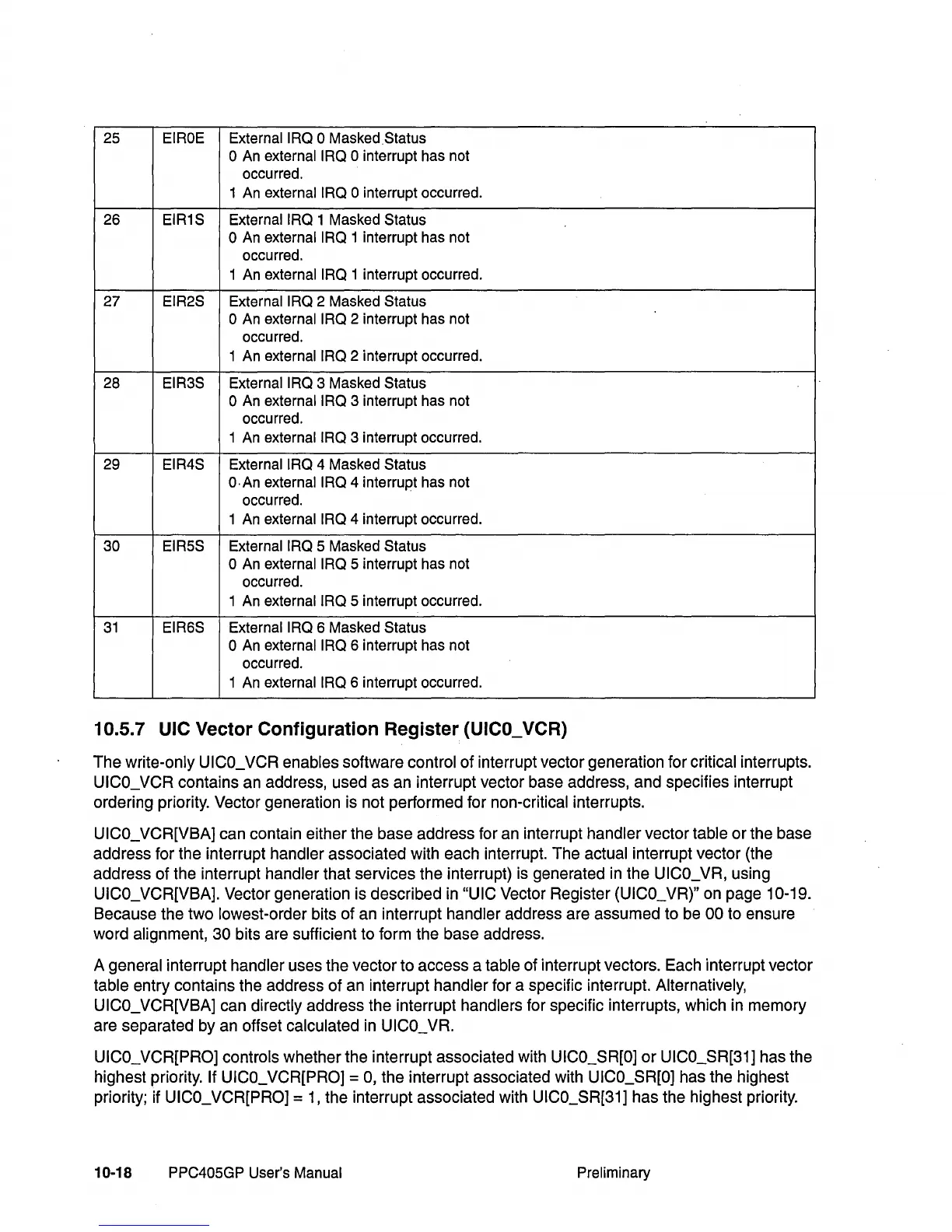

25

EIROE

External IRQ a Masked.Status

a

An

external IRQ a interrupt has not

occurred.

1

An

external IRQ a interrupt occurred.

26

EIR1S External IRQ 1 Masked Status

a

An

external IRQ 1 interrupt has not

occurred.

1 An external

IRQ 1 interrupt occurred.

27

EIR2S External IRQ 2 Masked Status

a An external IRQ 2 interrupt has not

occurred.

1 An external

IRQ 2 interrupt occurred.

28

EIR3S External IRQ 3 Masked Status

a

An

external IRQ 3 interrupt has not

occurred.

1

An

external IRQ 3 interrupt occurred.

29

EIR4S External IRQ 4 Masked Status

O·An external IRQ 4 interrupt has not

occurred.

1

An

external IRQ 4 interrupt occurred.

30 EIR5S External IRQ 5 Masked Status

a An external IRQ 5 interrupt has not

occurred.

1 An external

IRQ 5 interrupt occurred.

31

EIR6S External IRQ 6 Masked Status

a An external IRQ 6 interrupt has not

occurred.

1

An

external IRQ 6 interrupt occurred.

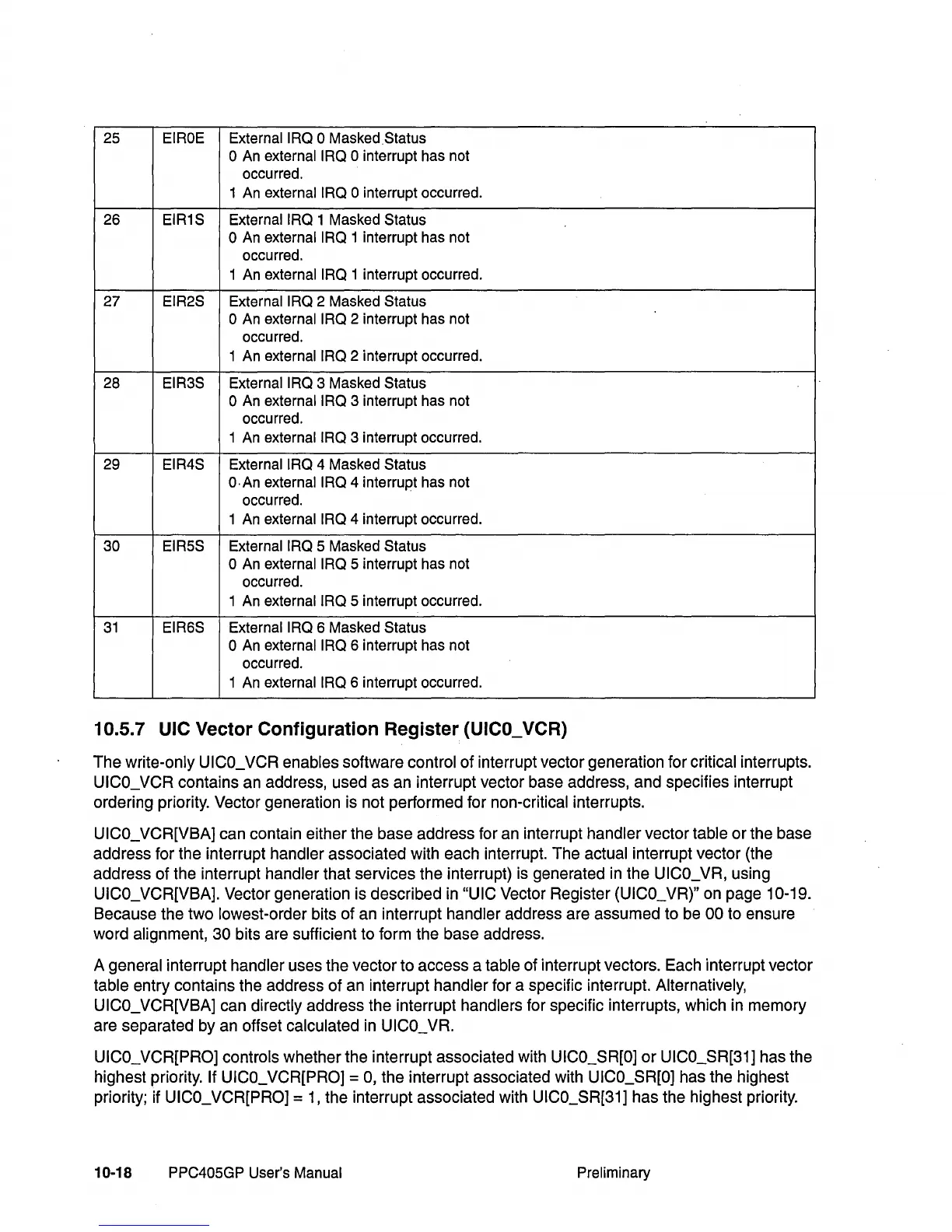

10.5.7 UIC Vector Configuration Register (UICO_ VCR)

The write-only UICO_ VCR enables software control

of

interrupt vector generation for critical interrupts.

UICO_VCR contains an address, used

as

an interrupt vector base address, and specifies interrupt

ordering priority.

Vector generation is not performed for non-critical interrupts.

UICO_ VCR[VBA] can contain either the base address for an interrupt handler vector table or the base

address for the interrupt handler associated with each interrupt. The actual interrupt vector (the

address of the interrupt handler that services the interrupt) is generated in the

UICO_ VR, using

UICO_VCR[VBA]. Vector generation is described in "UIC Vector Register (UICO_VR)" on page 10-19.

Because the two lowest-order bits

of

an interrupt handler address are assumed to be 00 to ensure

word alignment,

30 bits are sufficient to form the base address.

A general interrupt handler uses the vector to access a table of interrupt vectors. Each interrupt vector

table entry contains the address of an interrupt handler for a specific interrupt. Alternatively,

UICO_VCR[VBA] can directly address the interrupt handlers for specific interrupts, which in memory

are separated by an offset calculated in

UICO_ VA.

UICO_VCR[PRO]

controls whether the interrupt associated with UICO_SR[O]

or

UICO_SR[31] has the

highest priority.

If UICO_ VCR[PRO] = 0, the interrupt associated with UICO_SR[O] has the highest

priority; if

UICO_VCR[PRO] =

1,

the interrupt associated with UICO_SR[31] has the highest priority.

10-18

PPC405GP User's Manual

Preliminary

Loading...

Loading...