17.9

pel

Bridge Reset and Initialization

The following sections discuss resetting and initializing the PCI bridge.

17.9.1· Address Map Initialization

When the PCI bridge is the PCI master, it can generate memory,

110,

configuration, interrupt

acknowledge, and special cycles. The method of cycle generation, and the associated address

ranges, are fixed, except for memory cycles.

PCI memory cycles are generated when the PCI bridge

detects a cycle

in

one of three specified PLB address ranges. The sizes and address spaces of these

ranges are specified using the PMM registers. Also, the address of the resulting PCI memory cycle

can be an offset from the PLB address (address translation occurs). This translation is also specified

in the PMM registers. The PMM registers

do

notde1ault to usable values following reset; they must be

initialized before attempting to generate

PCI memory cycles.

When the

PCI bridge is a target on the PCI bus, the PCI bridge can respond to memory cycles. The

memory cycle address ranges that the

PCI bridge responds to are specified

in

PCICO_PTM1 BAR and

PCICO_PTM2BAR. These registers are typically initialized as part of the standard PCI initialization

process.

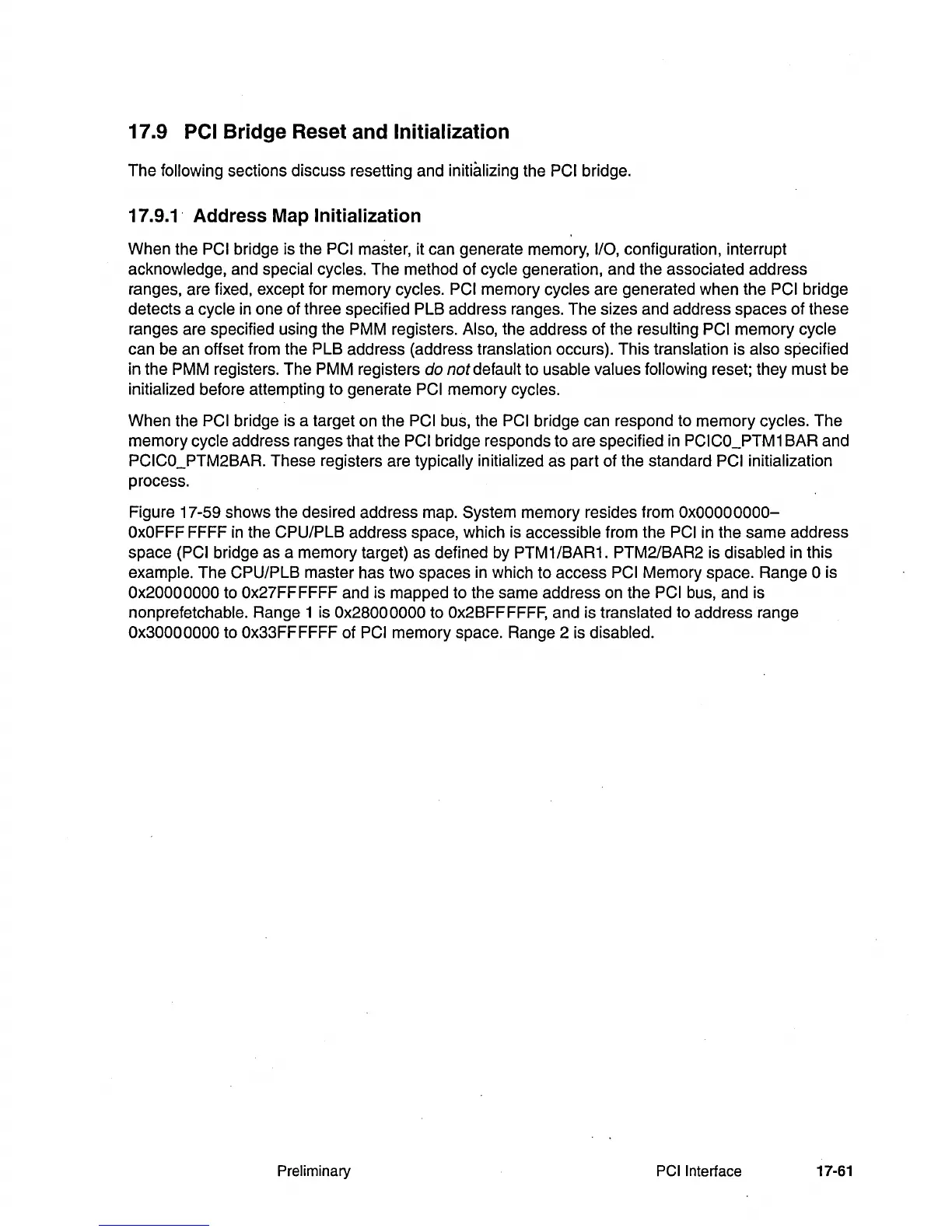

Figure 17-59 shows the desired address map. System memory resides from

OxOOOOOOOO-

OxOFFF

FFFF

in

the CPUlPLB address space, which is accessible from the PCI in the same address

space

(PCI bridge as a memory target) as defined

by

PTM1/BAR1. PTM2/BAR2 is disabled in this

example. The CPU/PLB master has two spaces

in

which to access PCI Memory space. Range 0 is

Ox20000000 to Ox27FFFFFF and is mapped to the same address on the PCI bus, and is

nonprefetchable. Range 1 is

Ox28000000 to Ox2BFFFFFF, and is translated to address range

Ox30000000 to Ox33FFFFFF of PCI memory space. Range 2 is disabled.

Preliminary

PCI Interface

17-61

Loading...

Loading...