16:19 BKnE Bank n Error

o

No

error

1 Error occurred

in

bank n

20:31 Reserved

15.4.6 Bus Error Address Register (SDRAMO_BEAR)

The SDRAM Bus Error Address Register (SDRAMO_BEAR) is a 32-bit register containing the

address of the access where a correctable

or

uncorrectable ECC error occurred. If the master that

initiated the transfer requested error locking, and the

SDRAMO_BEAR is not already locked, the

contents of

SDRAMO_BEAR are locked until the lock bit

in

one

of

the Peripheral Bus Error Status

Registers (SDRAMO_BESRO or SDRAMO_BESR1) is cleared. The contents of the SDRAMO_BEAR

are accessed indirectly through the SDRAM_CFGADDR and SDRAMO_CFGDATA registers using the

mfdcr

and

mtdcr

instructions.

SDRAMO

BEAR

+-

10

311

Figure

15-14.

Bus

Error

Address

Register

(SDRAMO_BEAR)

I

0:31

SDRAMO_BEAR

I Address

of

ECC

Error.

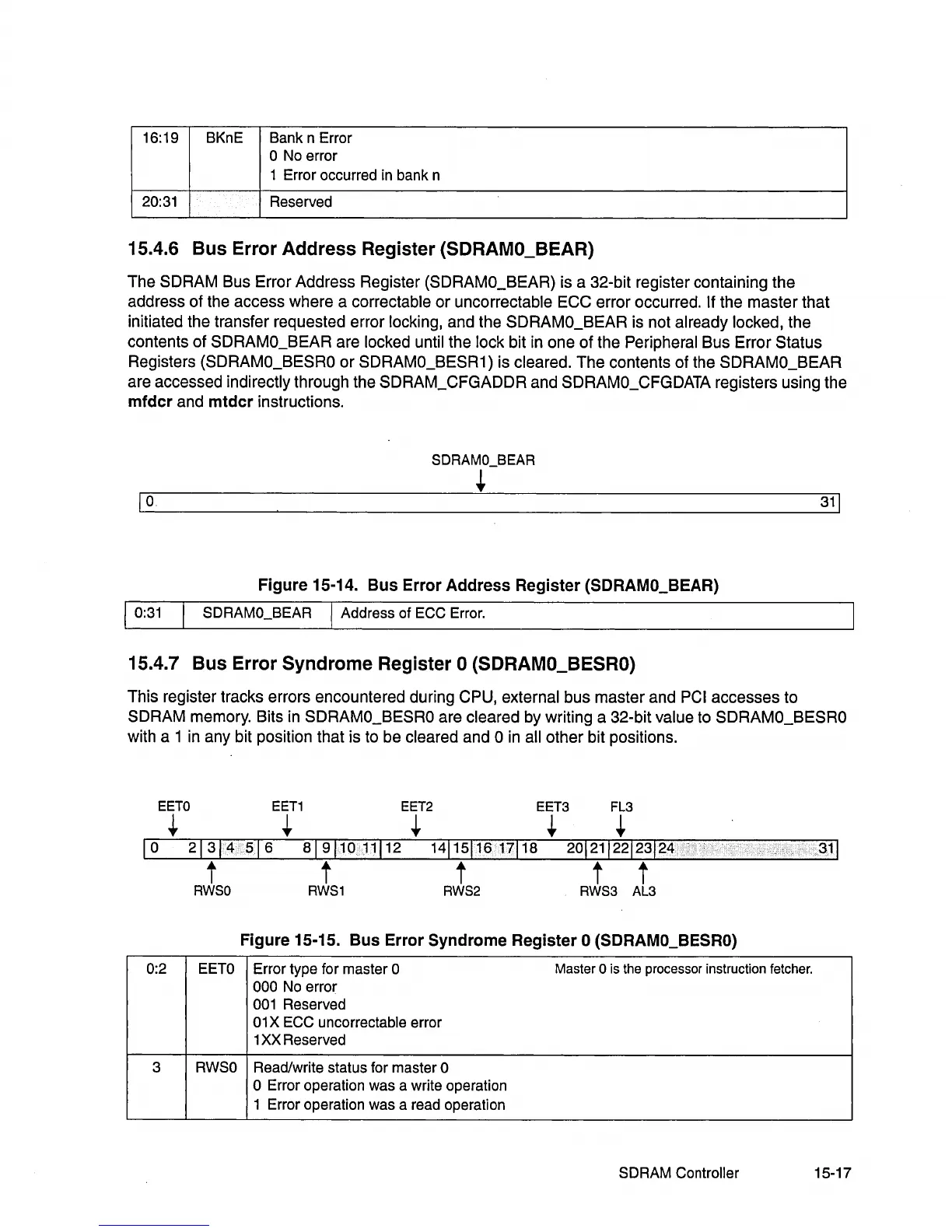

15.4.7 Bus Error Syndrome Register 0

(SDRAMO_BESRO)

This register tracks errors encountered during CPU, external bus master and

PCI

accesses to

SDRAM memory. Bits

in

SDRAMO_BESRO are cleared by writing a 32-bit value to SDRAMO_BESRO

with a 1

in

any bit position that is to be cleared and °

in

all other bit positions.

EETO

EET1

EET2

EET3

FL3

+

+ +

+ +

1

0

21314

51

6

81911011112

14115116

17

1

18

20121122123124

31

1

t

t t

t t

RWSO

RWS1

RWS2

RWS3

AL3

Figure

15-15.

Bus

Error

Syndrome

Register

0 (SDRAMO_BESRO)

0:2

EETO

Error type for master 0

Master

0

is

the

processor

instruction

fetcher.

000

No

error

001

Reserved

01

X

ECC

uncorrectable error

1

XX

Reserved

3

RWSO

Read/write status for master 0

o Error operation was a write operation

1 Error operation was a

read

operation

SDRAM Controller

15-17

Loading...

Loading...