• Independent, large (2 KB) transmit and (4 KB) receive FIFOs with programmable thresholds to

minimize overruns and underruns.

• Multiple packet handling

in

transmit and receive FIFOs.

•

Unicast, multicast, broadcast, and promiscuous address filtering capabilities.

•

Two

64-bit hash filters for unicast and multicast packets.

• Automatic retransmission of collided packets.

• Rejection of runt packets before providing them to MAL.

• Mil interface for connection to a variety of PHY layer devices.

• Programmable inter-packet gap to enable tuning for better system performance.

• Compliance with IEEE 802.3x standard packet-based flow control, including self-assembled control

pause packet transmitting.

• Support for VLAN tag ID

in

compliance with IEEE Draft 802.3ac/D1.0 standard.

• VLAN tag insertion or replacement for transmit packets is a programmable option.

• Wake On LAN (WOL) handling.

• Programmable internal

and external loop-back capabilities.

•

Extensive error/status vector generation for each processed packet.

• Power management using a clock and power management (CPM) unit.

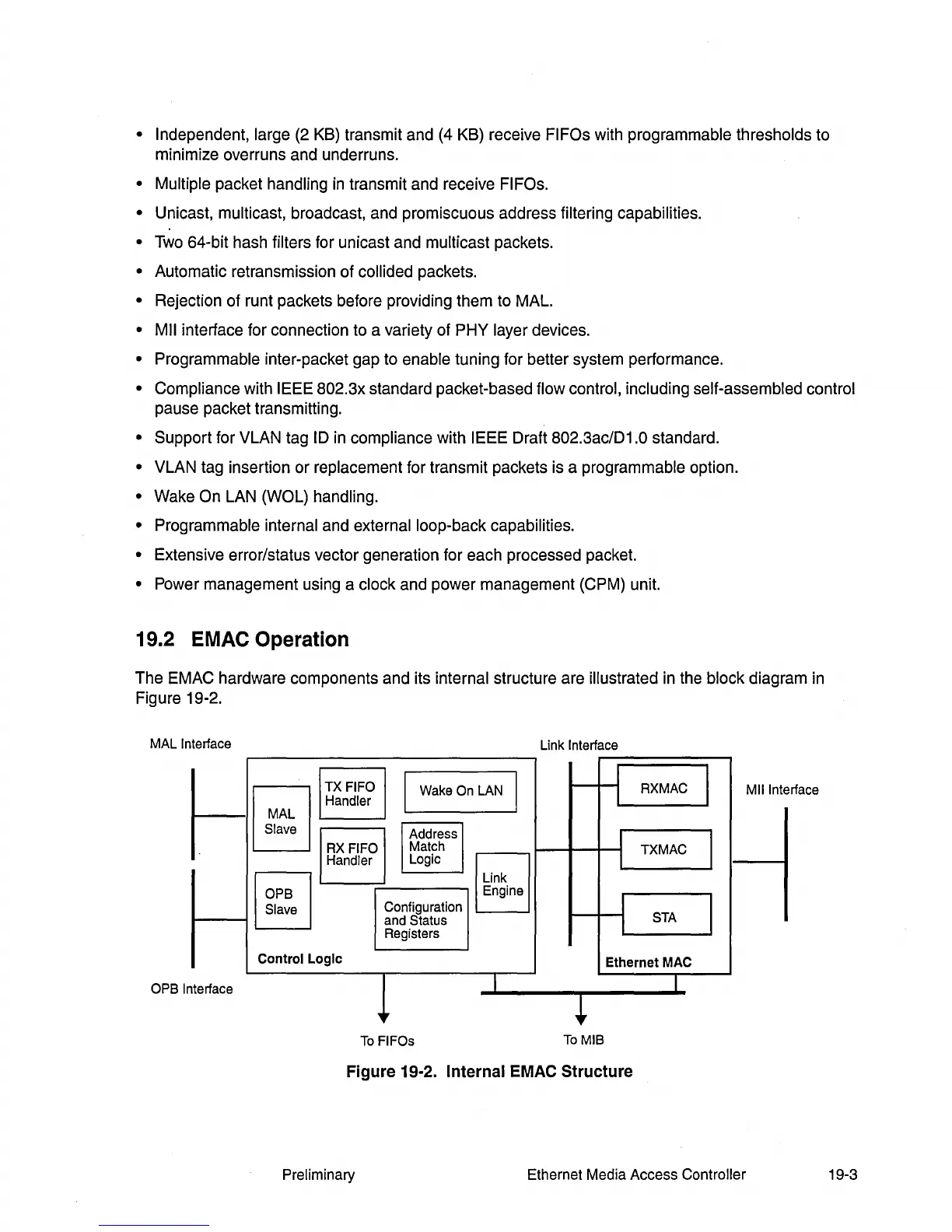

19.2

EMAC

Operation

The EMAC hardware components and its internal structure are illustrated

in

the block diagram

in

Figure 19-2.

MAL Interface

~

~"---'

~

RXFIFO

Handler

Wake On LAN

Control

Logic

OPS Interface

Configuration

and

Status

Registers

To

FIFOs

Link

Engine

Link

Interface

Ethernet MAC

To

MIS

Figure 19·2. Internal

EMAC

Structure

Preliminary

Ethernet Media Access Controller

Mil

Interface

19-3

Loading...

Loading...