5:4 MERE PLB Bus Error Response Enable MERE controls the response taken by the

00 No action is taken.

PCI bridge on the PCI bus (as the PCI

01

The PCI target should drive PCISErr on target) when PLB bus errors are asserted

the

PCI bus. to the PCI bridge PLB master.

10 Target should target abort the offending

Note:

Only reads can be target aborted.

read.

Note:

Modes

10

and

11

cannot be used in

11

Indicates the PCI target should drive asynchronous mode.

PCISErr and target abort.

3 MEDE PLB Master Error Detection Enable MEDE enables the detection of PLB bus

o Disables detection

of

PLB master errors. errors when the PCI bridge is a PLB

1 Enables detection of PLB master errors.

master.

2 MEAE PLB Bus Error Assertion Enable MEAE enables the reporting

of

a PLB bus

o Disabled error when the PCI bridge is a PLB slave.

1 Enabled

1

WDPE Write Data Parity

PCISErr Enable The PCI bridge drives PCISErr when a

o Disabled data parity error is detected on a write

1 Enabled.

cycle when the

PCI bridge is the PCI

target. PCICO_CMD[SE] must also be 1.

0 MAEE Master Abort Error Enable MAEE enables the detection of a master

o Disabled abort as an error condition when the PCI

1 Enabled

bridge is the master.

The

PCI bridge drives

SI_MErr on the PLB bus in response to a

master abort.

If this bit is disabled, driving

of

S,-Merr

in response to master abort is

masked.

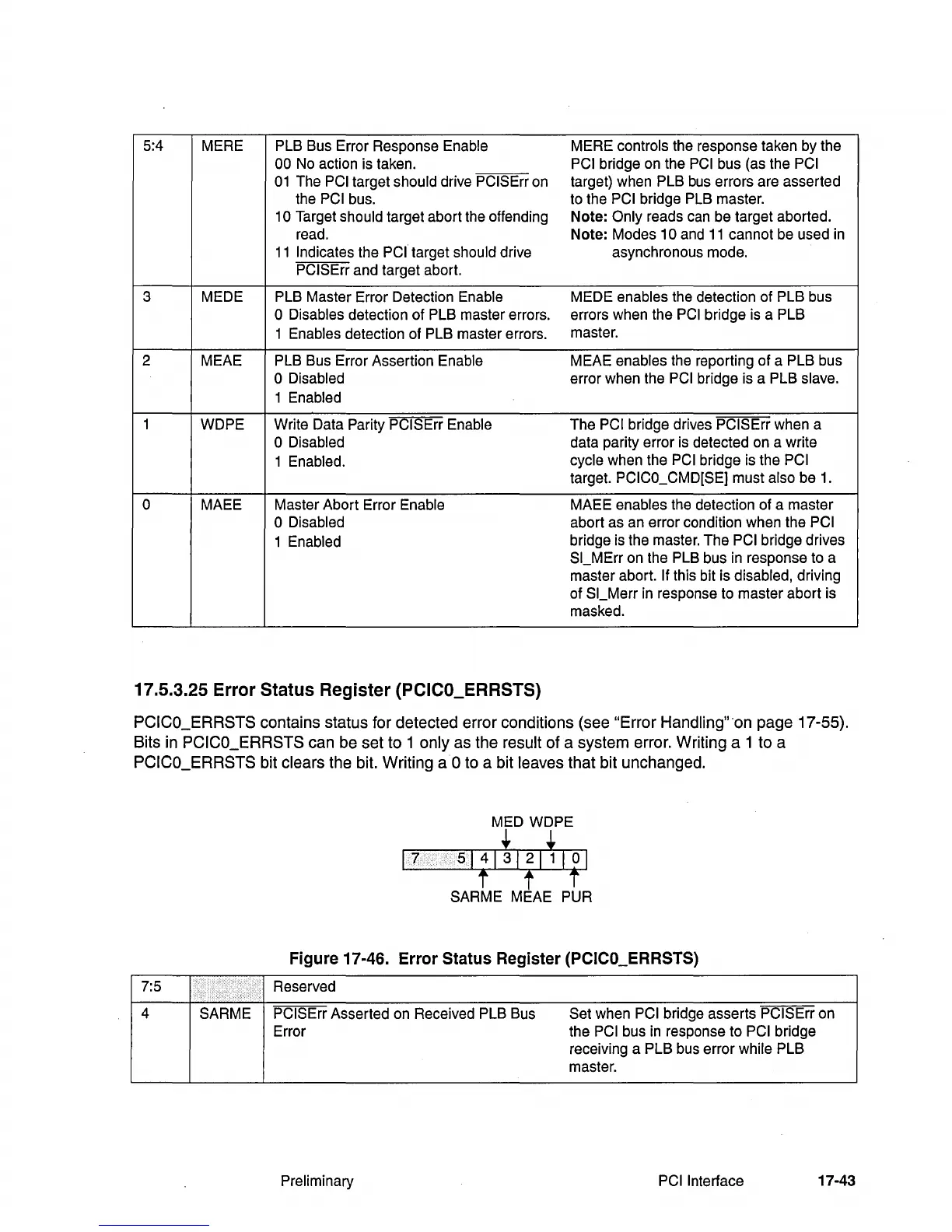

17.5.3.25 Error Status Register (PCICO_ERRSTS)

PCICO_ERRSTS contains status for detected error conditions (see "Error Handling" 'on page 17-55).

Bits in

PCICO_ERRSTS can be set to 1 only as the result of a system error. Writing a 1 to a

PCICO_ERRSTS bit clears the bit. Writing

aO

to a bit leaves that bit unchanged.

MED

WDPE

t

...

f f t

SARME MEAE PUR

Figure

17·46.

Error

Status

Register (PCICO_ERRSTS)

7:5

Reserved

4

SARME PCISErr Asserted on Received PLB Bus

Set when PCI bridge asserts PCISErr on

Error

the

PCI bus

in

response to PCI bridge

receiving a PLB bus error while PLB

master.

Preliminary

PCllnterface

17·43

Loading...

Loading...