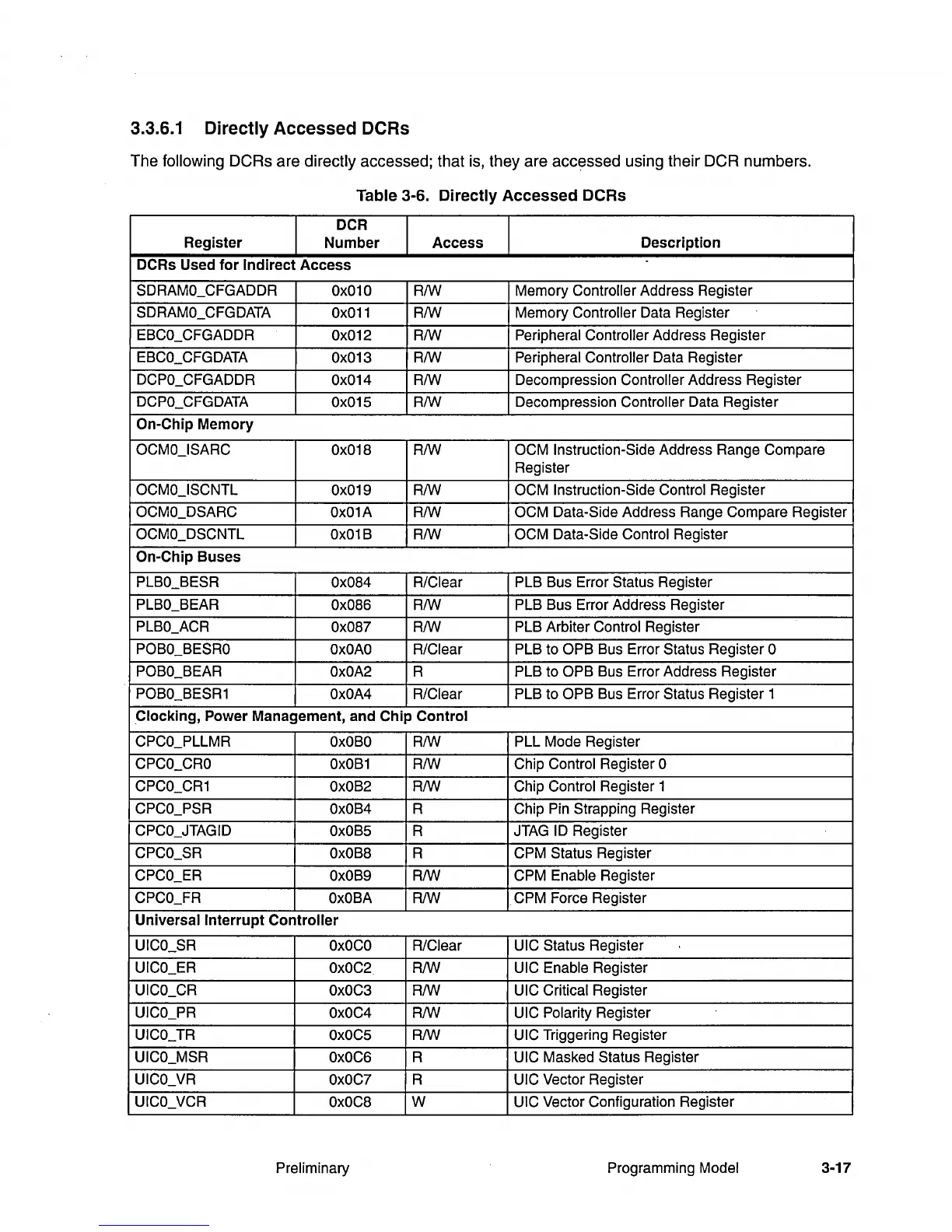

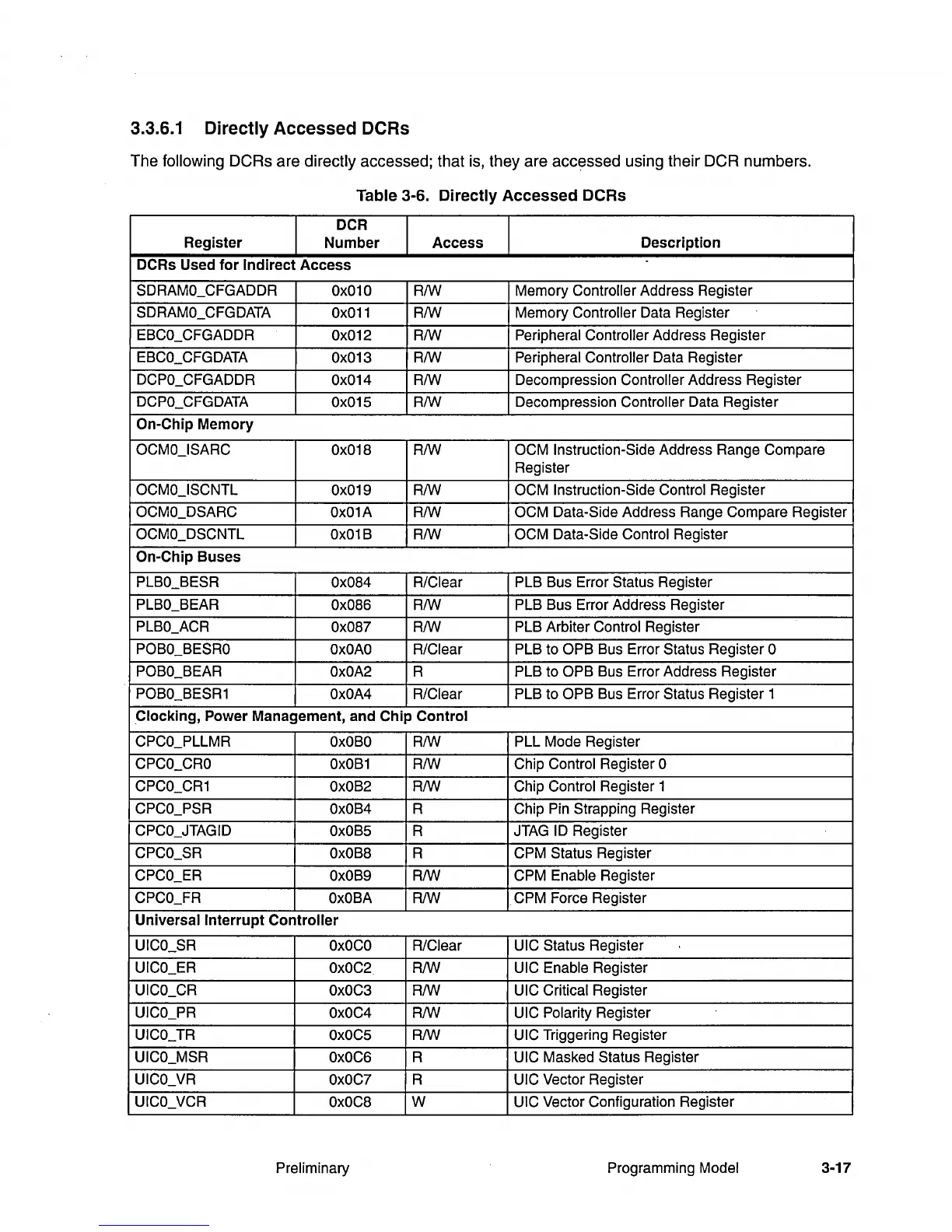

3.3.6.1 Directly Accessed DCRs

The following DCRs are directly accessed; that is, they are accessed using their OCR numbers.

Table 3-6. Directly Accessed DCRs

DCR

Register

Number

Access

Description

DCRs

Used

for

Indirect

Access

SDRAMO_CFGADDR

Ox010 RIW

Memory Controller Address Register

SDRAMO_CFGDATA

Ox011

RIW Memory Controller Data Register

EBCO_CFGADDR

Ox012 RIW

Peripheral

Controller Address Register

EBCO_CFGDATA

Ox013 RIW Peripheral Controller Data Register

DCPO_CFGADDR

Ox014 RIW

Decompression Controller Address Register

DC

PO_C

FG

DATA

Ox015

RIW

Decompression Controller Data Register

On-Chip

Memory

OCMO_ISARC

Ox018 RIW

OCM Instruction-Side Address Range Compare

Register

OCMO_ISCNTL

Ox019 RIW OCM Instruction-Side Control

Register

OCMO_DSARC

Ox01A RIW OCM

Data-Side Address Range Compare Register

OCMO_DSCNTL

Ox01B RIW

OCM Data-Side Control Register

On-Chip

Buses

PLBO_BESR

Ox084 R/Clear PLB

Bus Error Status Register

PLBO_BEAR

Ox086 RIW

PLB

Bus Error Address Register

PLBO_ACR

Ox087 RIW PLB

Arbiter Control Register

POBO_BESRO

OxOAO

R/Clear

PLB

to OPB Bus Error Status Register 0

POBO_BEAR

OxOA2

R

PLB to OPB Bus Error Address Register

POBO_BESR1

OxOA4

R/Clear

PLB

to OPB Bus Error Status Register 1

Clocking,

Power

Management,

and

Chip

Control

CPCO_PLLMR

OxOBO

RIW PLL Mode Register

CPCO_CRO

OxOB1

RIW Chip Control Register 0

CPCO_CR1

OxOB2

RIW Chip Control Register 1

CPCO_PSR

OxOB4

R

Chip

Pin Strapping Register

CPCO_JTAGID

OxOB5

R

JTAG

ID Register

CPCO_SR

OxOB8

R

CPM Status Register

CPCO_ER

OxOB9

RIW

CPM Enable

Register

CPCO_FR

OxOBA

R/W

CPM Force Register

Universal

Interrupt

Controller

UICO_SR

OxOCO

R/Clear

UIC Status

Register

UICO_ER

OxOC2

RIW UIC Enable Register

UICO_CR

OxOC3

RIW

UIC Critical

Register

UICO_PR

OxOC4

RIW

UIC Polarity

Register

UICO_TR

OxOC5

RIW UIC Triggering Register

UICO_MSR

OxOC6

R UIC Masked Status Register

UICO_VR

OxOC7

R UIC Vector Register

UICO_VCR

OxOC8

W UIC Vector Configuration Register

Preliminary

Programming Model

3-17

Loading...

Loading...