5:6 DRW SDRAM Width Must be set to

2'bOO.

0032-bit

01

Reserved

10 Reserved

11

Reserved

7:8

BRPF Burst Read Prefetch Granularity Most applications should set with field to

00 Reserved 2'b01.

01

16 bytes

1032

bytes

11

Reserved

9

ECCDD

ECC Driver

Disable

Regardless

of whether ECC checking is

o Check bit data output

on

ECC7:0. enabled, SDRAM writes cause the

1

ECC7:0 are placed

in

high-Z state.

PPC405GP to output check bit data

on

ECC7:0. If ECC is not used, setting

ECCDD=1

disables these drivers.

10 EMDULR Enable Memory Data Unless Read

o MemDataO:31 are high-Z unless a

memory write is being performed.

1 MemDataO:31 are driven

unless a

memory read is being performed.

11

:31

}(""',

'.>":',

Reserved

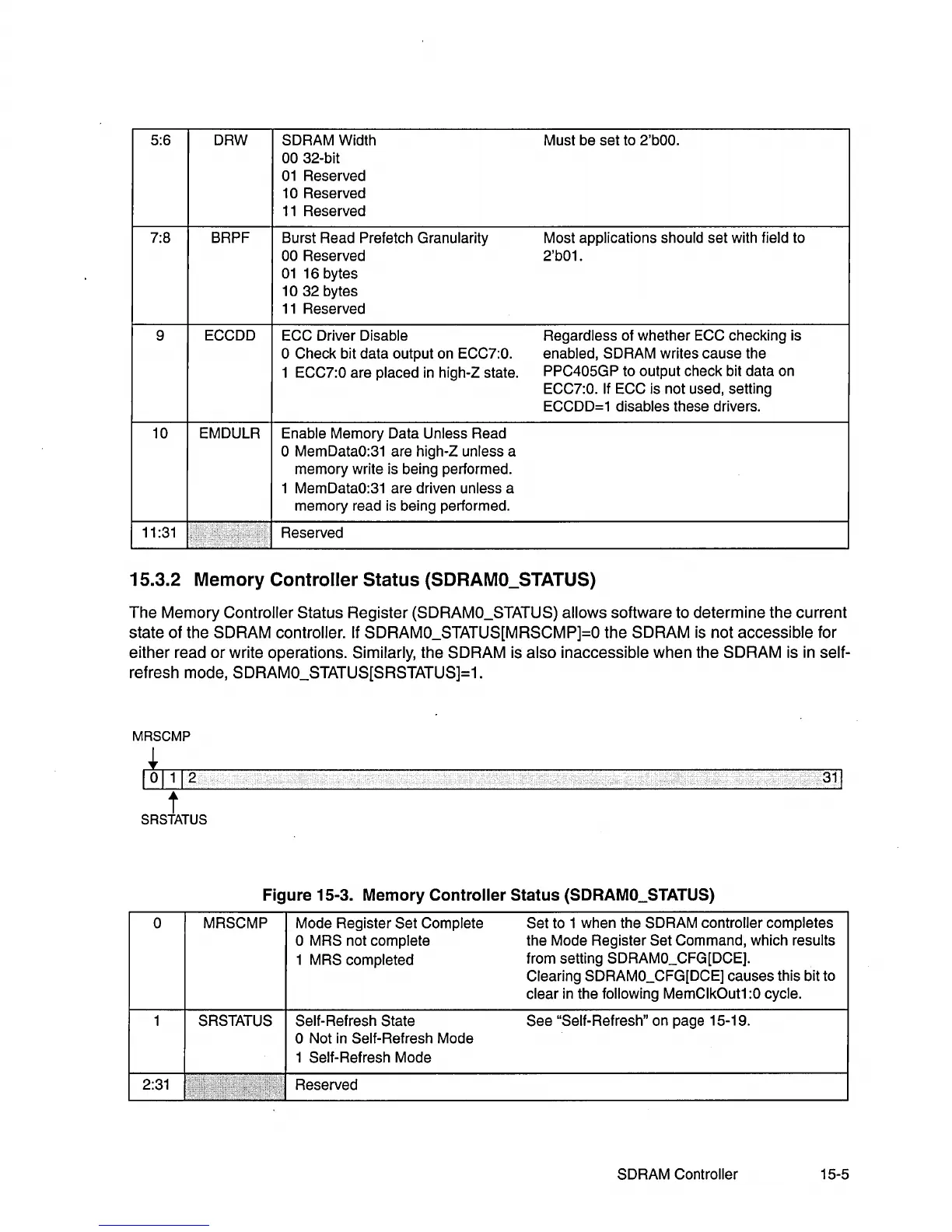

15.3.2 Memory Controller Status (SDRAMO_STATUS)

The

Memory

Controller

Status

Register

(SDRAMO_STATUS)

allows

software

to

determine

the

current

state

of

the

SDRAM

controller. If

SDRAMO_STATUS[MRSCMP]=O

the

SDRAM

is

not

accessible

for

either

read

or

write

operations.

Similarly,

the

SDRAM

is

also

inaccessible

when

the

SDRAM

is in

self-

refresh

mode,

SDRAMO_STATUS[SRSTATUS]=1.

MRSCMP

+

31

1

t

SRSTATUS

Figure 15-3. Memory Controller Status (SDRAMO_STATUS)

o

2:31

MRSCMP Mode Register Set Complete

o MRS not complete

1 MRS completed

SRSTATUS Self-Refresh State

o Not

in

Self-Refresh Mode

1 Self-Refresh Mode

Reserved

Set to 1 when the SDRAM controller completes

the Mode Register Set Command, which results

from setting SDRAMO_CFG[DCE].

Clearing SDRAMO_CFG[DCE]

causes this bit to

clear

in

the following MemClkOut1:0 cycle.

See "Self-Refresh"

on page 15-19.

SDRAM Controller

15-5

Loading...

Loading...