17.3.3

PCI

Target Map Configuration

Two PCI bridge address ranges

in

PCI memory space are mapped to PLB space: PCI target map

(PTM1) and PTM2

(PTMO

is reserved).

Each PTM is configured using the

following registers (n is 1

or

2,

corresponding with PTM1 and

PTM2,

respectively).

•

PTMnMemory Size (PCILO_PTMnMS)

• PTMnLocal

Address (PCILO_PTMnLA)

•

PTMnBAR (PCILO_PTMnBAR)

The size of each PTM is programmable, using the PCILO_PTMnMS registers. The size is a power of

2,

and ranges from

4KB-4GB.

The PLB and PCI address spaces for each PTM are aligned to this

size

..

The address range of PLB space accessed through each PTM is also programmable, enabling

address translation between the PCI bus and the PLB. The PLB address range is defined

in

the

PCILO_PTMnLA registers.

The

location of each PTM

in

PCI memory space is programmable, using the PCIPCILO_PTMnBAR

registers.

The PTMs are

enabled and disabled using PCICO_CMD[MA]. PTM address ranges and sizes should

be initialized before being enabled. If the PCI bridge is not the host bridge, the local processor must

initialize the PTM size before enabling host configuration setting the Host Configuration Enable (HCE)

field of the Bridge Options 2 register (PCICO_BRDGOPT2). This ensures that the host experiences

proper behavior from the

PCILO_PTMnBAR registers. Note that PTM1 is always enabled. The PTM1

registers must

always be initialized.

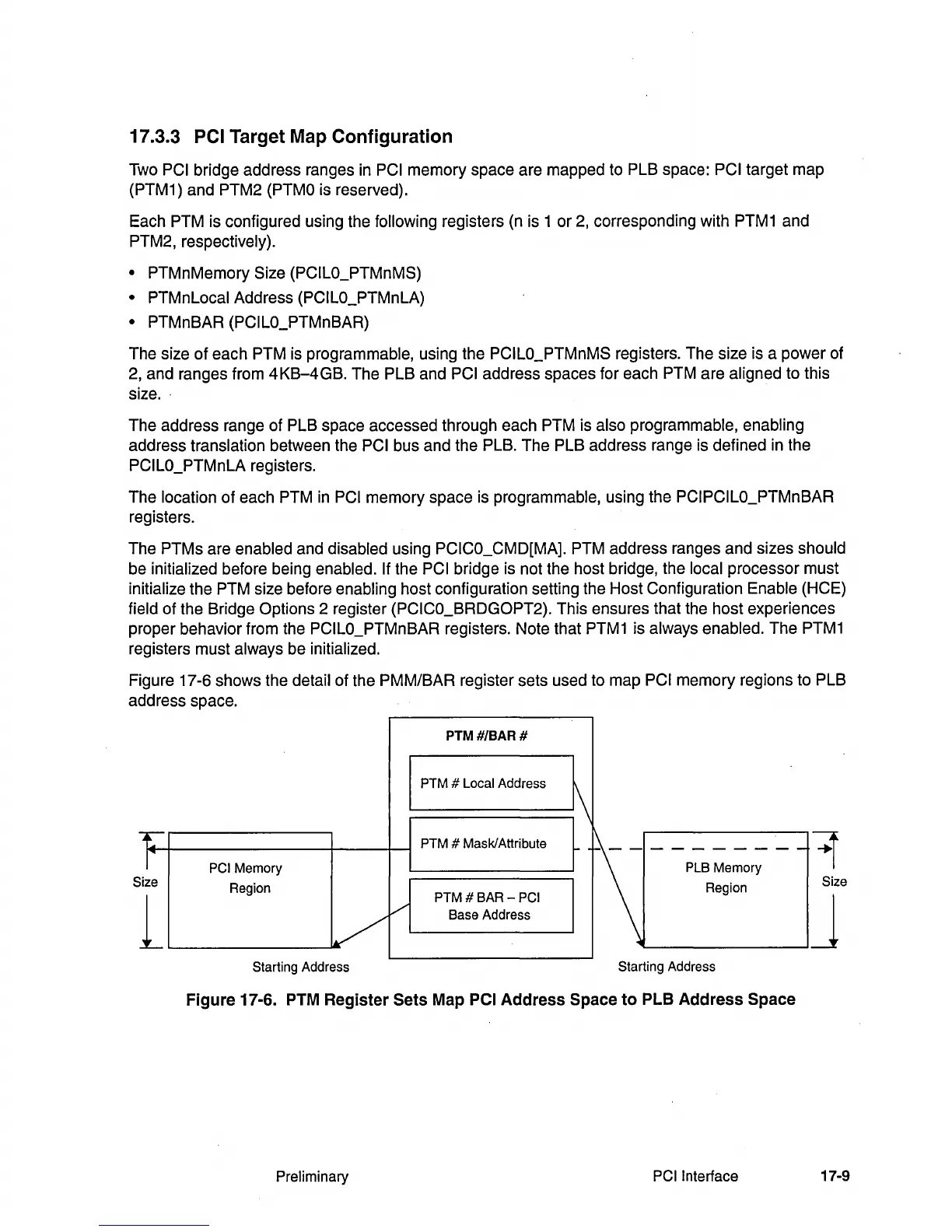

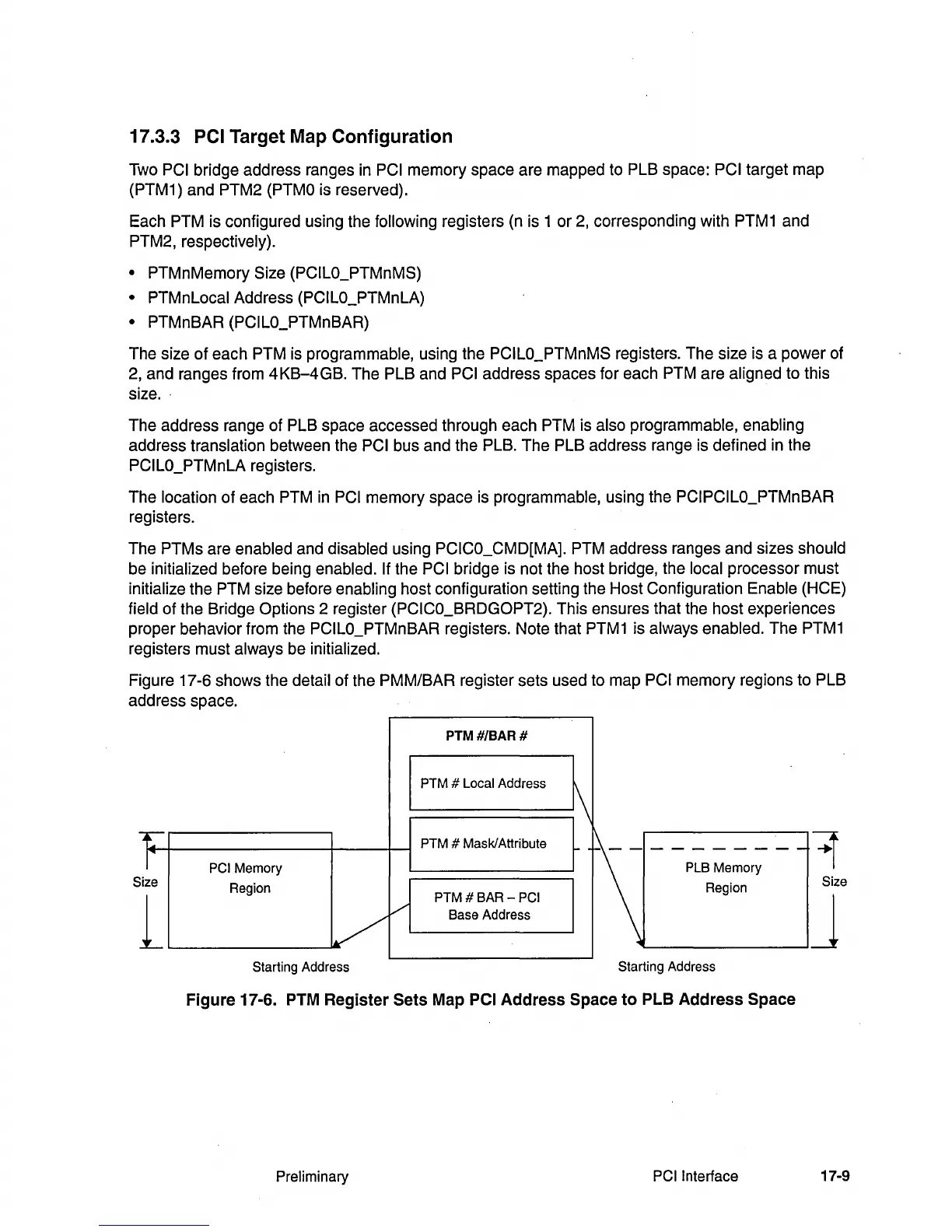

Figure 17-6 shows the detail of the PMM/BAR register sets used to map PCI memory regions to PLB

address space.

PTM#/BAR#

PTM # Local Address

~

S

~

PTM # Mask/Attribute

t-

\

--------

I

PCI Memory

PLB Memory

ize

Region

1

Region

1

PTM # BAR - PCI

V

Base Address

1

Size

J

Starting Address

Starting Address

Figure 17-6.

PTM

Register Sets Map

PCI

Address Space

to

PLB Address Space

Preliminary

PCI Interface

17-9

Loading...

Loading...