2.1.1 PLB Features

• Overlapping of read and write transfers allows two data transfers per clock cycle for maximum bus

utilization

•

Decoupled address and data buses support split-bus transaction capability for improved bandwidth

• Address pipelining reduces overall bus latency by allowing the latency associated with a new

request to be overlapped with an ongoing data transfer

in

the same direction

• Late master request abort capability reduces latency associated with aborted requests

• Four levels of request priority and selectable arbitration modes provide flexible arbitration policies.

• Support for 16-, 32-, and 64-byte line data transfers

• Sequential burst protocol allows byte, halfword, and word burst data transfers.

• DMA buffered peripheral-to-memory, memory-to-peripheral, and memory-to-memory operations

are supported

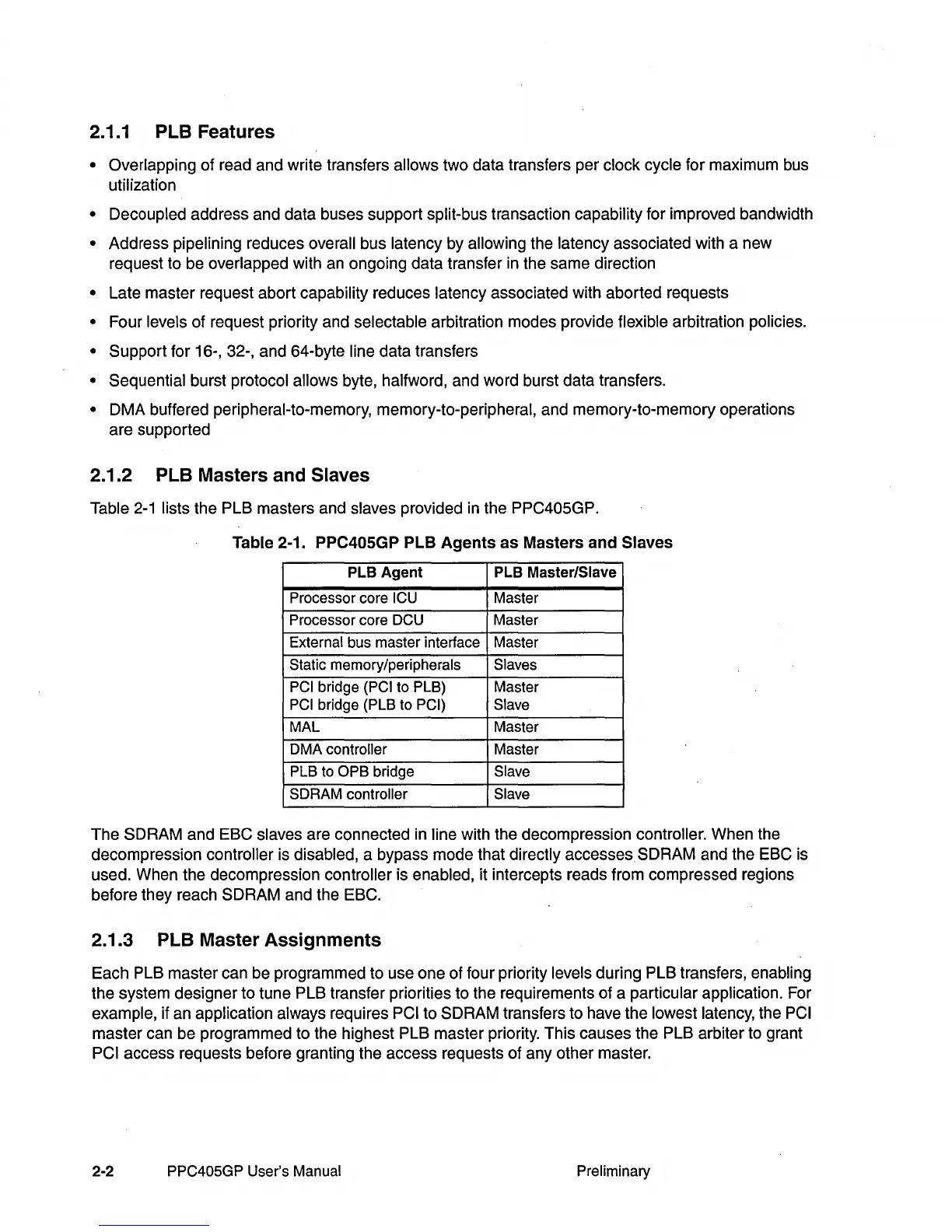

2.1.2 PLB Masters and Slaves

Table

2-1

lists the PLB masters and slaves provided

in

the PPC405GP.

Table 2-1. PPC405GP

PLB

Agents

as

Masters

and

Slaves

PLB

Agent

PLB

Master/Slave

Processor core ICU Master

Processor core DCU Master

External bus master interface Master

Static memory/peripherals Slaves

PCI

bridge (PC I to PLB) Master

PCI bridge (PLB to PCI) Slave

MAL Master

DMA

controller Master

PLB to OPB bridge Slave

SDRAM controller Slave

The SDRAM and EBC slaves are connected in line with the decompression controller. When the

decompression

controller is disabled, a bypass mode that directly

accesses

SDRAM and the EBC is

used. When the decompression

controller is enabled, it intercepts reads from compressed regions

before they reach SDRAM and the EBC.

2.1.3 PLB Master

Assignments

Each PLB master can be programmed to use one of four priority levels during PLB transfers, enabling

the system designer to tune PLB transfer priorities to the requirements of a particular application. For

example, if an

application always requires PCI to SDRAM transfers to have the lowest latency, the PCI

master can be programmed to the highest PLB master priority. This causes the PLB arbiter to grant

PCI access requests before granting the access requests of any other master.

2-2 PPC405GP User's Manual

Preliminary

Loading...

Loading...