relative to other EBC operations. Internal to the PPC405GP all reads and

writes

that target the

EBC

are assigned the priority

Ob1

o.

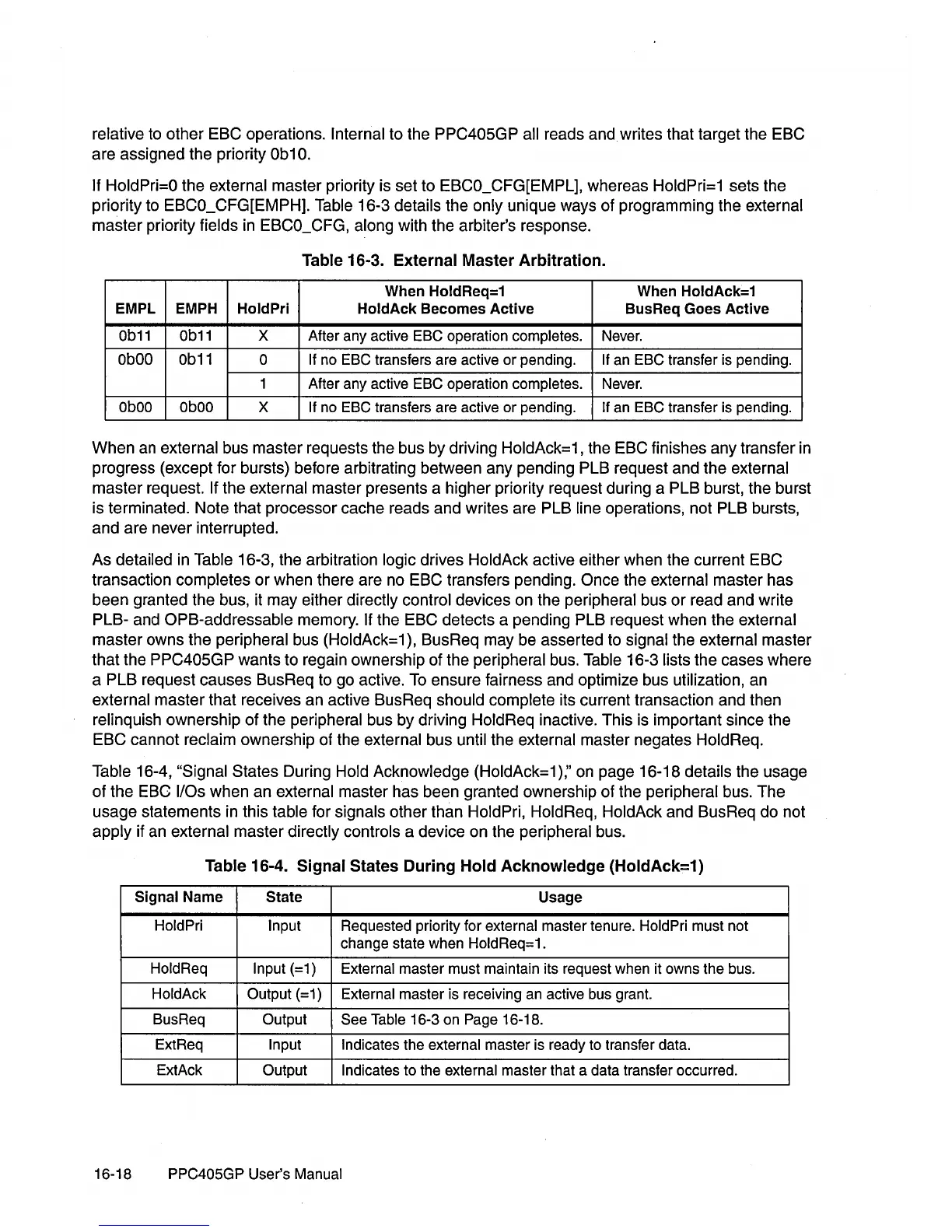

If HoldPri=O the external master priority is set to EBCO_CFG[EMPL], whereas HoldPri=1 sets the

priority to EBCO_CFG[EMPH]. Table 16-3 details the only unique ways of programming the external

master

priority fields in EBCO_CFG, along with the arbiter's response.

Table 16-3. External Master Arbitration.

When HoldReq=1 When HoldAck=1

EMPL

EM

PH

HoldPri

HoldAck

Becomes Active

BusReq Goes Active

Ob11

Ob11

X After

any

active

ESC

operation completes.

Never.

ObOO

Ob11

0

If

no

ESC

transfers

are

active or pending.

If

an

ESC

transfer

is

pending.

1 After

any

active

ESC

operation completes.

Never.

ObOO

ObOO

X

If

no

ESC

transfers

are

active

or

pending. If

an

ESC

transfer

is

pending.

When

an external bus master requests the bus by driving HoldAck=1 , the EBC finishes any transfer in

progress (except for bursts) before arbitrating between any pending PLB request and

the

external

master

request. If the external master presents a higher priority request during a PLB burst, the burst

is terminated. Note that processor cache reads and writes are PLB line operations, not PLB bursts,

and are never interrupted.

As

detailed in Table 16-3, the arbitration logic drives HoldAck active either when the current EBC

transaction completes

or

when there are no EBC transfers pending. Once the external master has

been granted the bus, it may either directly control devices on the peripheral bus

or

read and write

PLB- and OPB-addressable memory. If the EBC detects a pending PLB request when the external

master

owns the peripheral bus (HoldAck=1), BusReq may be asserted to signal the external master

that the

PPC405GP wants to regain ownership of the peripheral bus. Table 16-3 lists the cases where

a PLB request causes BusReq to go active.

To

ensure fairness and optimize bus utilization, an

external master that receives an active BusReq should complete its current transaction and then

relinquish ownership of the peripheral bus

by

driving HoldReq inactive. This is important since the

EBC

cannot reclaim ownership of the external bus until the external master negates HoldReq.

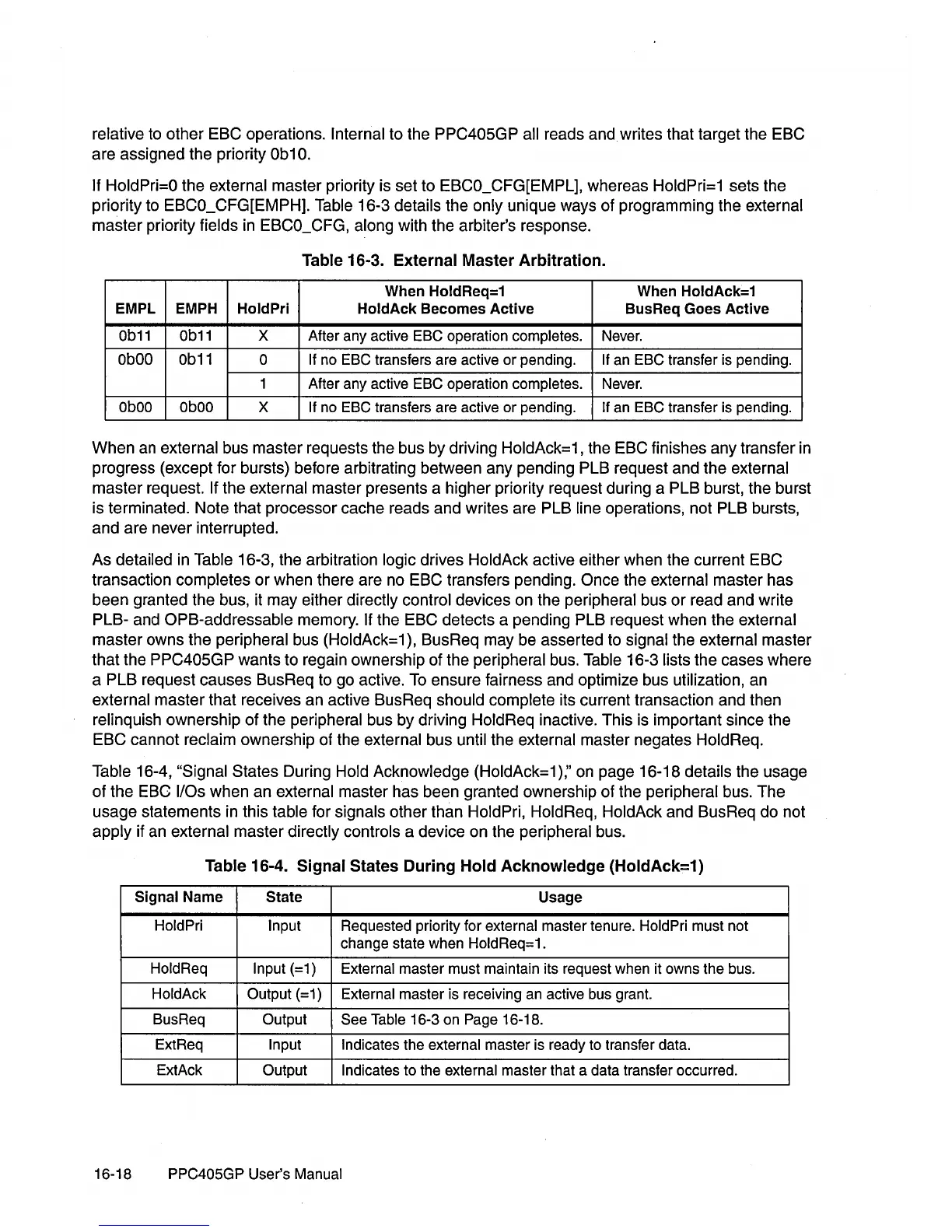

Table 16-4, "Signal States During Hold Acknowledge (HoldAck=1):' on page 16-18 details the usage

of

the

ESC liDs

when

an external master has been granted ownership of the peripheral bus.

The

usage statements in this table for signals other than HoldPri, HoldReq, HoldAck and BusReq do not

apply if an external master directly controls a device on the peripheral bus.

Table 16-4. Signal States During Hold Acknowledge (HoldAck=1)

Signal Name

State Usage

HoldPri Input

Requested priority for external master tenure. HoldPri must not

change state

when

HoldReq=1.

HoldReq

Input

(=1)

External master must maintain its request

when

it

owns

the

bus.

HoldAck

Output(=1) External master

is

receiving

an

active

bus

grant.

SusReq

Output

See

Table

16-3

on

Page

16-18.

ExtReq

Input Indicates the external master

is

ready

to

transfer

data.

ExtAck Output

Indicates

to

the

external master that a data transfer occurred.

16-18 PPC405GP User's Manual

Loading...

Loading...