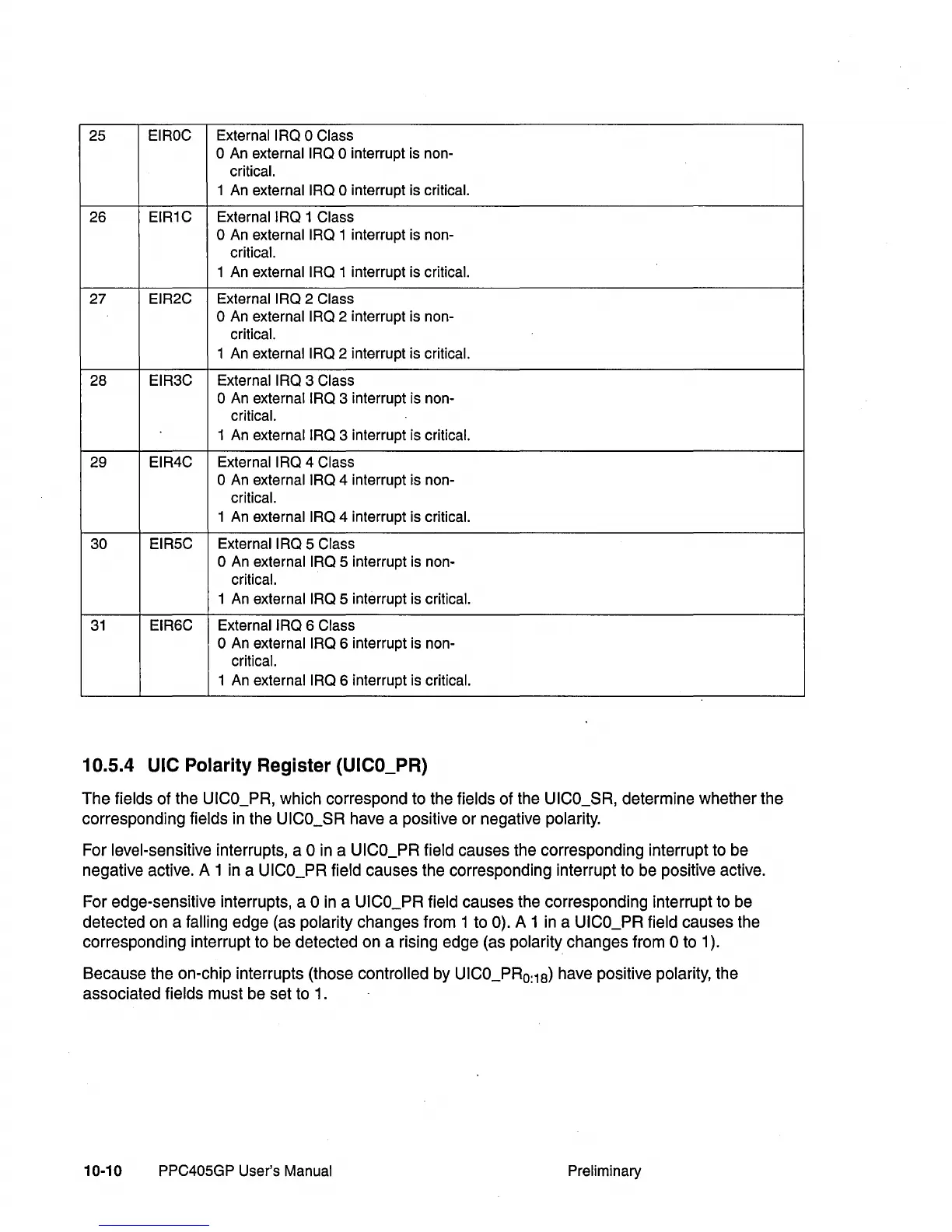

25

EIROC

External IRQ 0 Class

o

An

external IRQ 0 interrupt is non-

critical.

1

An

external IRQ 0 interrupt is critical.

26

EIR1C

External IRQ

1 Class

o

An

external IRQ 1 interrupt is non-

critical.

1

An

external IRQ 1 interrupt is critical.

27

EIR2C

External IRQ

2 Class

o

An

external IRQ 2 interrupt is non-

critical.

1

An

external IRQ 2 interrupt is critical.

28 EIR3C External IRQ 3 Class

o

An

external IRQ 3 interrupt is non-

critical.

1

An

external IRQ 3 interrupt is critical.

29

EIR4C

External IRQ

4 Class

o

An

external IRQ 4 interrupt is non-

critical.

1

An

external IRQ 4 interrupt is critical.

30 EIR5C External IRQ

5 Class

o

An

external IRQ 5 interrupt is non-

critical.

1

An

external IRQ 5 interrupt is critical.

31

EIR6C External IRQ 6 Class

o

An

external IRQ 6 interrupt is non-

critical.

1

An

external IRQ 6 interrupt is critical.

10.5.4 UIC Polarity Register (UICO_PR)

The fields

of

the

UICO_PR,

which

correspond

to

the

fields

of

the

UICO_SR,

determine whether

the

corresponding fields

in

the

UICO_SR

have

a positive

or

negative

polarity.

For

level-sensitive interrupts, a °

in

a

UICO_PR

field

causes

the

corresponding interrupt

to

be

negative

active.

A 1

in

a

UICO_PR

field

causes

the

corresponding interrupt

to

be

positive

active.

For

edge-sensitive interrupts, a °

in

a

UICO_PR

field

causes

the

corresponding interrupt

to

be

detected

on

a falling

edge

(as

polarity changes

from

1

to

0).

A 1

in

a

UICO_PR

field

causes

the

corresponding interrupt

to

be

detected

on

a rising

edge

(as

polarity changes

from

°

to

1).

Because

the

on-chip interrupts (those controlled

by

UICO_PR

o

:

18

)

have

positive

polarity,

the

associated fields

must

be

set

to

1.

10-10 PPC405GP User's Manual Preliminary

Loading...

Loading...