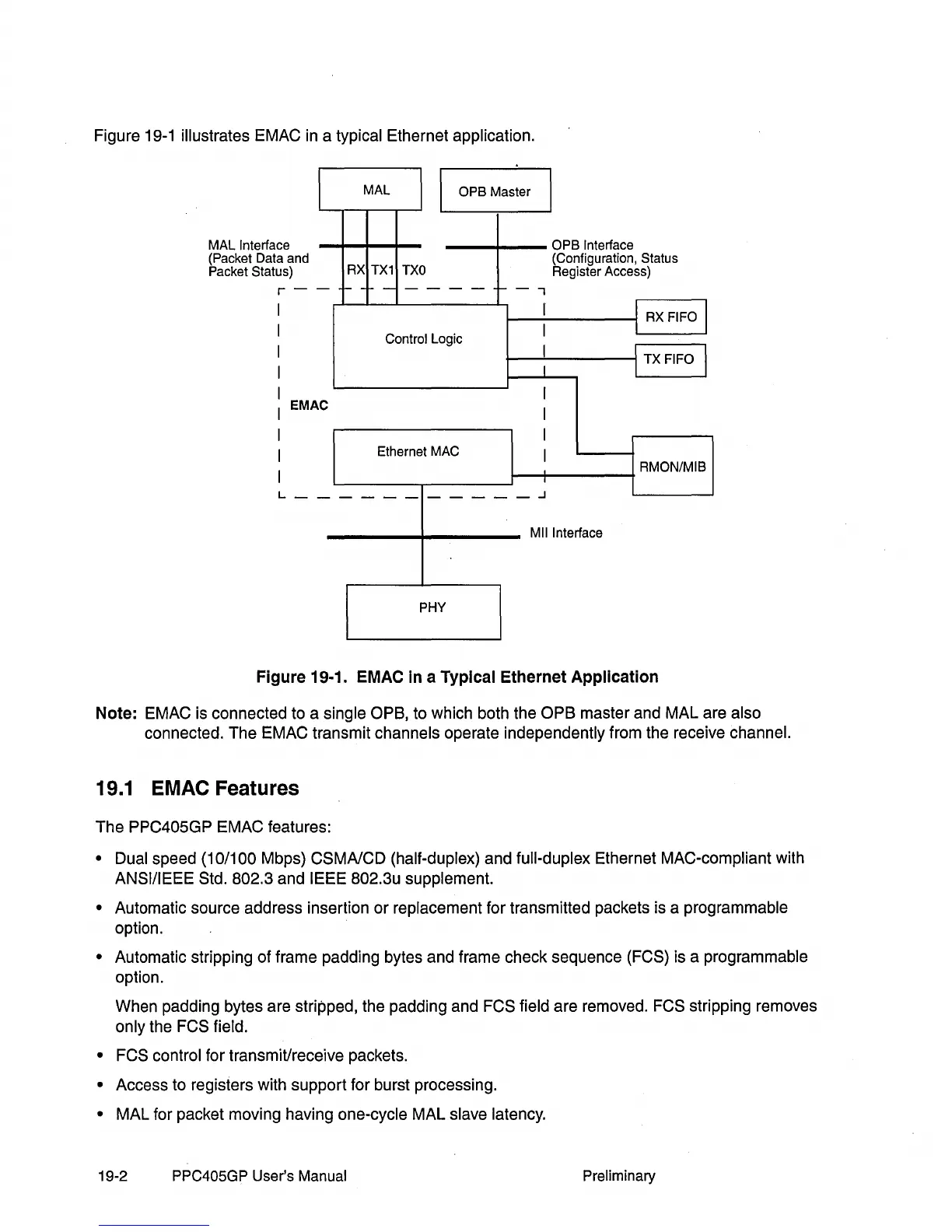

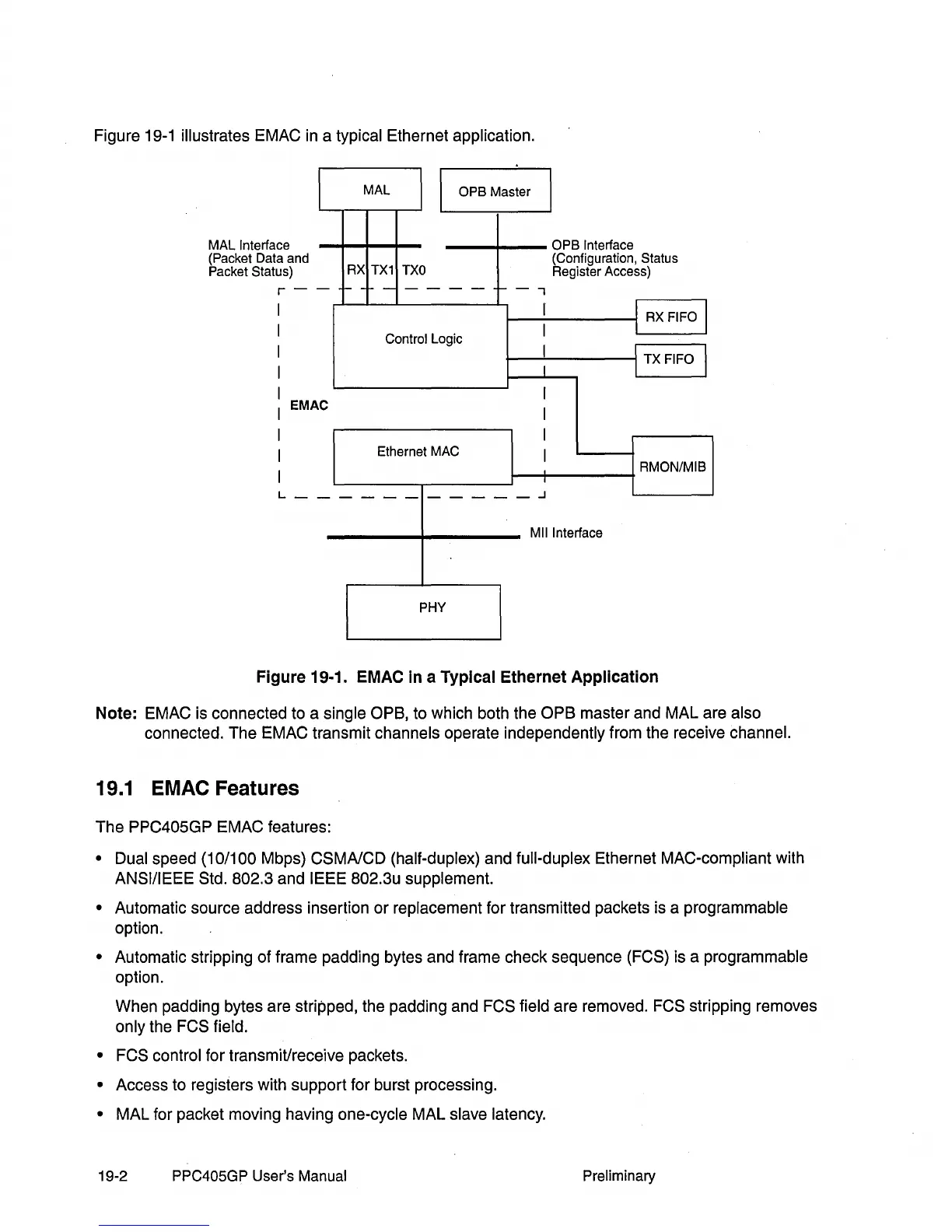

Figure

19-1

illustrates EMAC

in

a typical Ethernet application.

MAL Interface

(Packet Data and

Packet

Status)

r-

~

-

EMA

c

MAL

I

I

OPS Master

RX

TX1

TXO

I-

-

- -

--

I-

-

-,

I

I

Control Logic

I

I

I

I

I

Ethernet MAC

I

I

L_

- - -

--

_____

.J

I

OPS Interface

(Configuration, Status

Register Access)

! RX FIFO I

I

TX

FIFO I

RMON/MIS

Mil Interface

PHY

Figure 19·1.

EMAC

In

a Typical Ethernet Application

Note: EMAC is connected to a single OPS, to which both the OPS master and MAL are also

connected. The EMAC transmit channels operate independently from the receive channel.

19.1

EMAC

Features

The PPC405GP EMAC features:

• Dual speed (10/100 Mbps) CSMAlCD (half-duplex) and full-duplex Ethernet MAC-compliant with

ANSI/IEEE Std. 802.3 and IEEE 802.3u supplement.

• Automatic source address insertion or replacement for transmitted packets is a programmable

option.

• Automatic stripping of frame padding bytes and frame check sequence (FCS) is a programmable

option.

When padding bytes are stripped, the padding and

FCS field are removed. FCS stripping removes

only the

FCS field.

• FCS control for transmit/receive packets.

• Access to registers with support for burst processing.

• MAL for packet moving having one-cycle MAL slave latency.

19-2

PPC405GP User's Manual

Preliminary

Loading...

Loading...