Table 18·2. DMA Controller Configuration and Status Registers (continued)

Mnemonic

DCRAddress

Access

Description

Page

DMAO_DA2

Ox112 RIW DMA Destination Address Register 2 18-11

DMAO_SA2 Ox113 RIW

DMA

Source Address Register 2 18-10

DMAO_SG2 Ox114 RIW

DMA Scatter/Gather Descriptor Address Register 2

18-12

DMAO_CR3 Ox118 RIW

DMA Channel Control Register 3 18-8

DMAO_CT3 Ox119 RIW

DMA Count Register 3

18-11

DMAO_DA3

Ox11A

RIW

DMA Destination Address Register 3 18-11

DMAO_SA3 Ox11B

RIW

DMA Source Address Register 3 18-10

DMAO_SG3

Ox11C RIW

DMA Scatter/Gather Descriptor Address Register 3 18-12

DMAO_SR Ox120

R/Clear

DMA Status Register 18-7

DMAO_SGC

Ox123 RIW

DMA Scatter/Gather Command Register 18-13

DMAO_SLP

Ox12S

RIW DMA Sleep Mode Register 18-6

DMAO_POL

Ox126 RIW

DMA Polarity Configuration Register 18-S

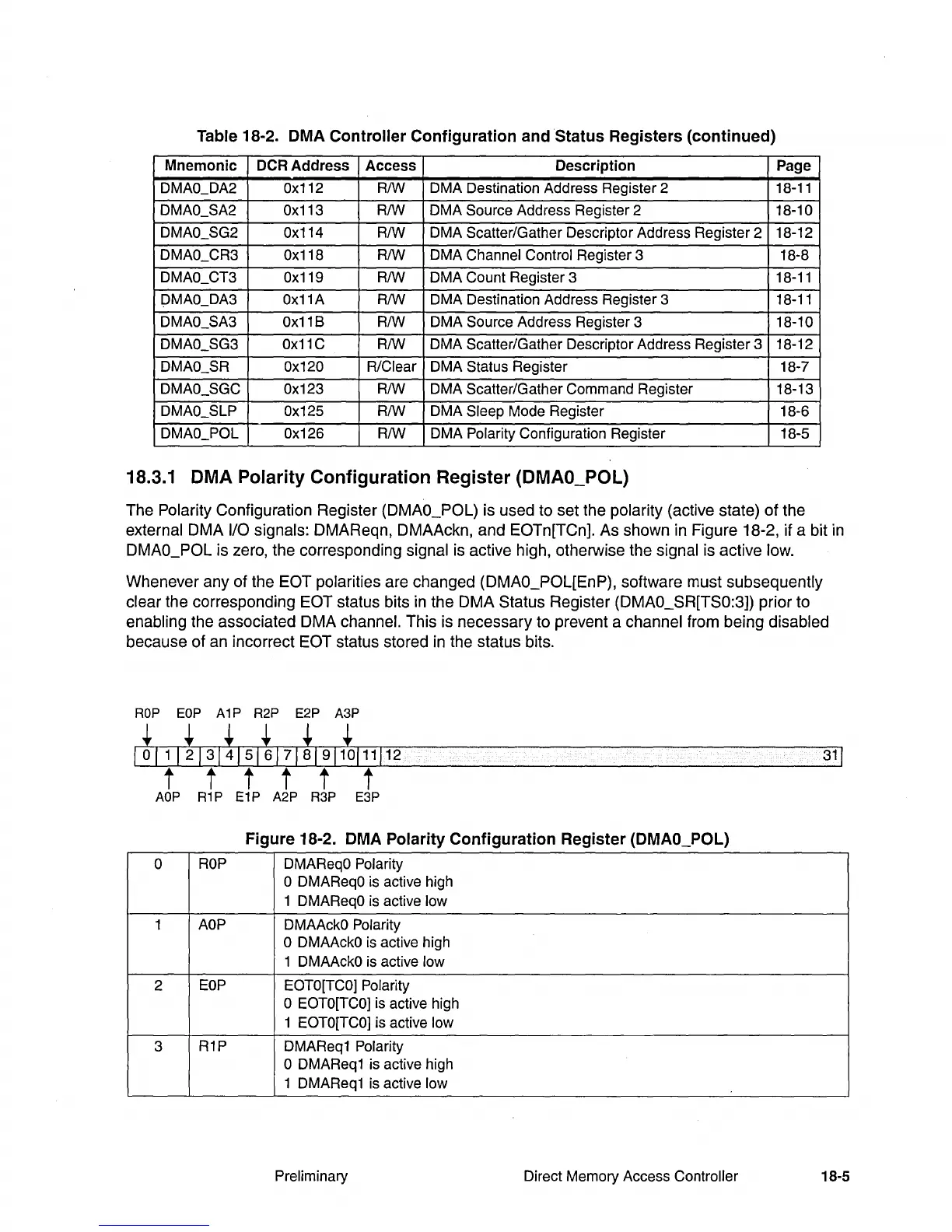

18.3.1 DMA Polarity Configuration Register (DMAO_POL)

The Polarity Configuration Register (DMAO_POL) is used to set the polarity (active state) of the

external DMA

1/0

signals: DMAReqn, DMAAckn, and EOTn[TCn]. As shown in Figure 18-2, if a bit

in

DMAO_POL is zero, the corresponding signal is active high, otherwise the signal is active low.

Whenever any of the EOT polarities are changed (DMAO_POL[EnP), software must subsequently

clear the corresponding EOT status bits

in

the DMA Status Register (DMAO_SR[TSO:3]) prior to

enabling the associated DMA channel. This is necessary to prevent a channel from being disabled

because of an incorrect EOT status stored

in

the status bits.

ROP

EOP

A 1 P R2P E2P A3P

t + * + + +

1

0

111213141s16171819110111112

3

1

/

t t t t t t

AOP

R1

P

E1

P A2P R3P E3P

Figure 18·2. DMA Polarity Configuration Register (DMAO_POL)

0

ROP

DMAReqO Polarity

o DMAReqO is active high

1

DMAReqO is active low

1

AOP

DMAAckO Polarity

o DMAAckO is active high

1

DMAAckO is active low

2

EOP

EOTO[TCO] Polarity

o EOTO[TCO] is active high

1

EOTO[TCO] is active low

3

R1P DMAReq1

Polarity

o DMAReq1 is active high

1 DMAReq1 is active

low

Preliminary

Direct Memory Access Controller 18-S

Loading...

Loading...