5.4.2 OCM Instruction-Side Control Register (OCMO_ISCNTL)

OCMO_ISCNTL enables and disables instruction-side OCM access and controls whether instruction

requests are satisfied

in

one or two cycles.

OCMO_ISCNTL[ISEN] enables

the OCM controller to respond to requests for instruction fetches to

addresses

in

the instruction-side OCM address range defined by OCMO_ISARC[ISAR]. At reset,

OCMO_ISCNTL[ISEN] =

0;

instruction-side OCM is not enabled. If instruction-side OCM is to be

accessed, this

field must be set to 1 during chip initialization, as described

in

"OCM Initialization" on

page 8-13.

Setting

OCMO_ISCNTL[ISTCM] = 1 places the instruction-side OCM

in

a mode

in

which accesses

complete in no fewer than two cycles. Two-cycle mode is provided for chips that cannot make

instruction-side timing to the processor core. The

PPC405GP, however, meets the timing

requirement. At reset,

OCMO_ISCNTL[ISTCM] =

1.

This field should be set to ° during chip

initialization so that instruction-side accesses can complete

in

one cycle. OCMO_ISCNTL[ISTCM]

does not affect data-side OCM operation.

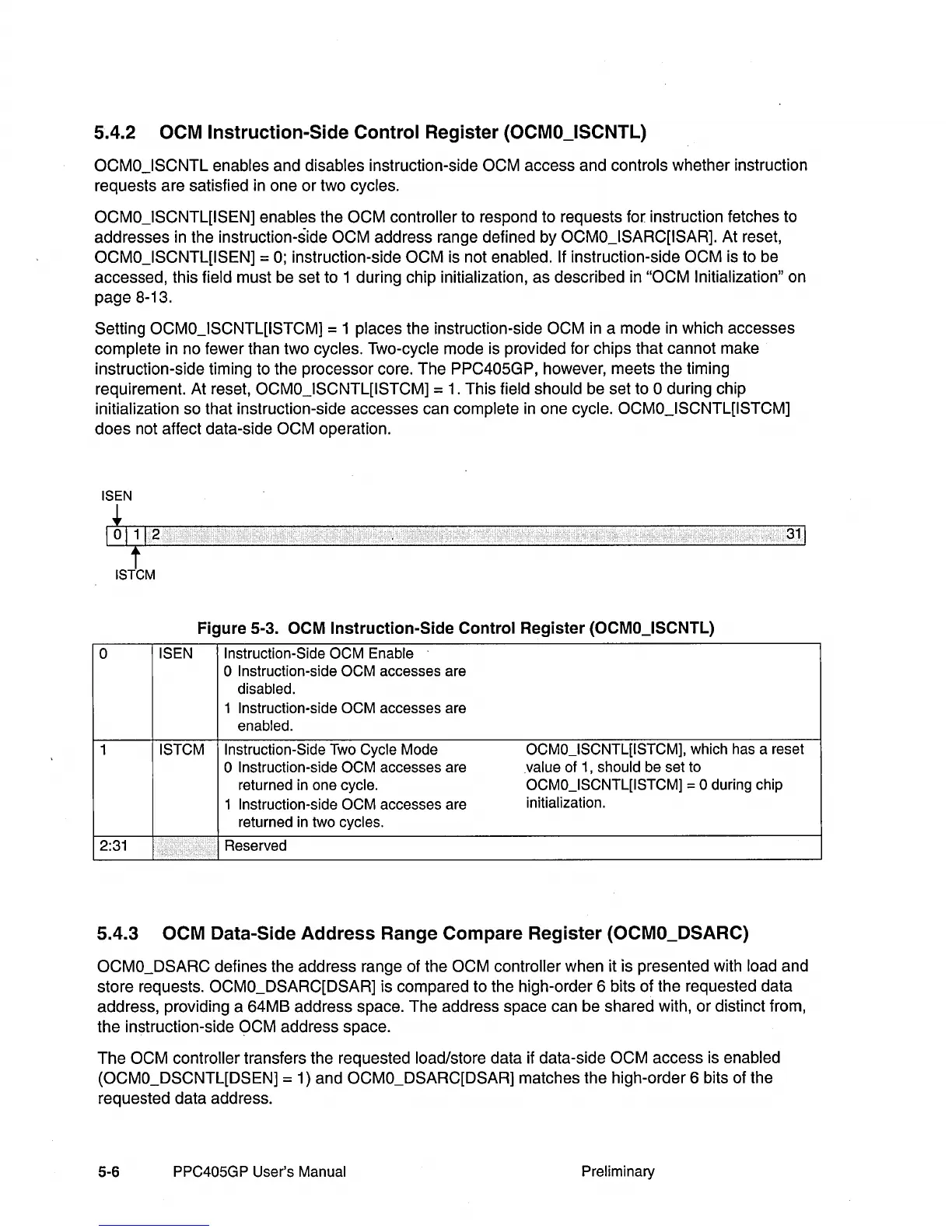

ISEN

+

3

1

1

t

ISTeM

Figure 5-3.

OCM

Instruction-Side Control Register (OCMO_ISCNTL)

0

ISEN Instruction-Side OCM Enable

o Instruction-side OCM accesses are

disabled.

1 Instruction-side OCM accesses are

enabled.

1 ISTCM

Instruction-Side

Two

Cycle Mode

OCMO_ISCNTL[ISTCM], which has a reset

o Instruction-side OCM accesses are

value of

1,

should be set to

returned

in

one cycle.

OCMO_ISCNTL[ISTCM] = 0 during chip

1 Instruction-side

OCM accesses are

initialization.

returned

in

two cycles.

2:31 Reserved

5.4.3 OCM Data-Side Address Range Compare Register (OCMO_DSARC)

OCMO_DSARC defines the address range of the OCM controller when it is presented with load and

store requests.

OCMO_DSARC[DSAR] is compared to the high-order 6 bits of the requested data

address, providing a 64MB address space. The address space can be shared with, or distinct from,

the instruction-side

OCM address space.

The

OCM controller transfers the requested load/store data if data-side OCM access is enabled

(OCMO_DSCNTL[DSEN]

= 1) and OCMO_DSARC[DSAR] matches the high-order 6 bits of the

requested data address.

5-6 PPC405GP User's Manual

Preliminary

Loading...

Loading...