Consider a scenario where such a situation causes store data to be held

in

the store data queue. If

any of the loads access the same address as the address of the store operation whose data is being

held in the store data queue, there is a need to bypass the store data from the store data queue to

provide the correct data to the

load operation.

A bypass is determined to be required by comparing the pending store address with the

load address.

However, the comparison is done with a 16KB address representation for the

load and store

operations, not the 4KB address (the physical size of the

PPC405GP OCM array). If the 16KB

address compares, the store data is bypassed to the

load operation. This implies that a bypass

results for address

aliasing only when the OCM addresses match at a 16KB multiple, which

corresponds to a match of address bits 18:29 (a word address that is further specified by byte

enables). Although the physical address space is aliased at 4KB

multiples, the bypass determination

is made at 16KB

multiples. Therefore, if bits 18: 19 of an aliased load address do not match bits 18: 19

of the 16KB store address of the data being

held in the store data queue, the load data will not be

coherent.

Instead of returning the most recently stored data, which is being held

in

the store data

queue, the

load returns "old" data previously stored in and accessed from the OCM array.

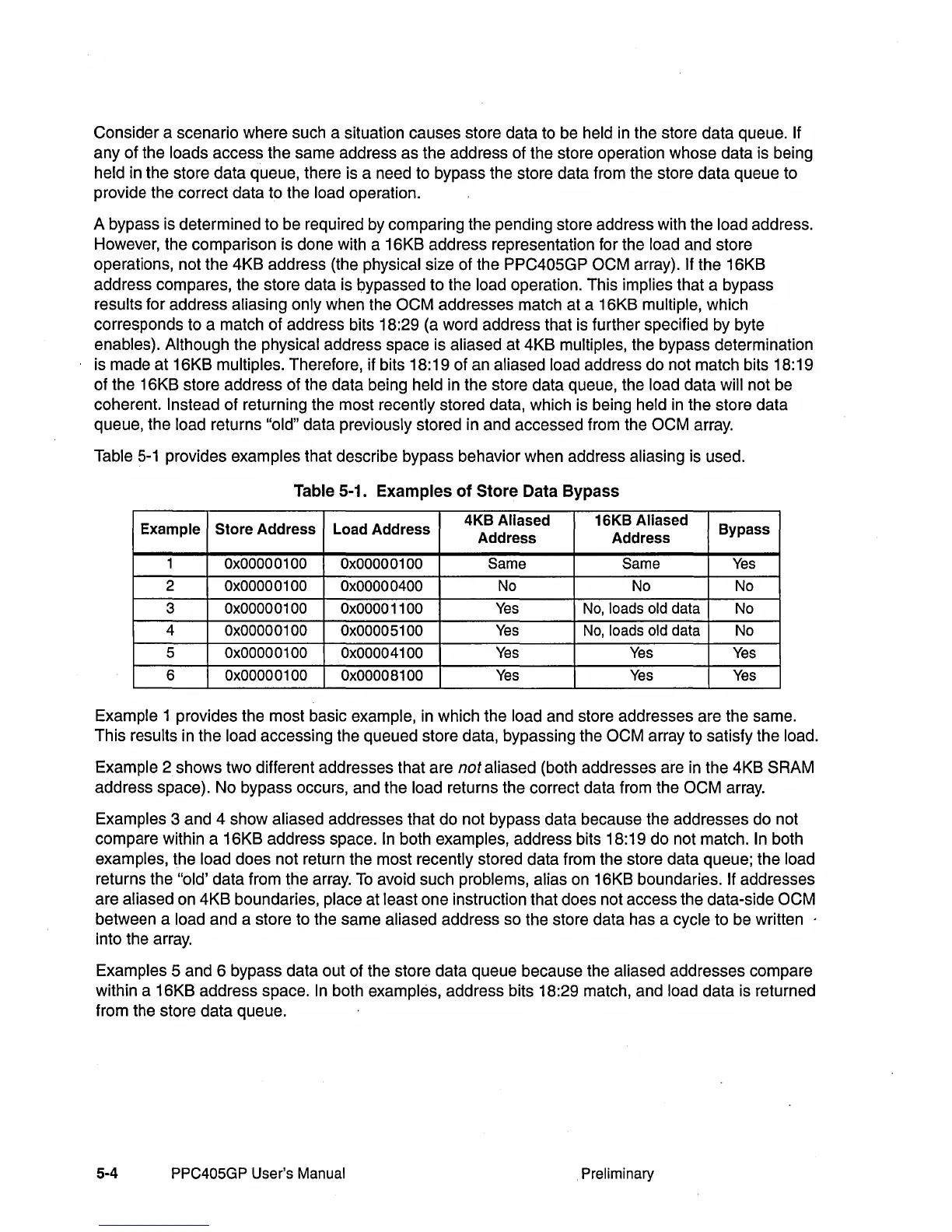

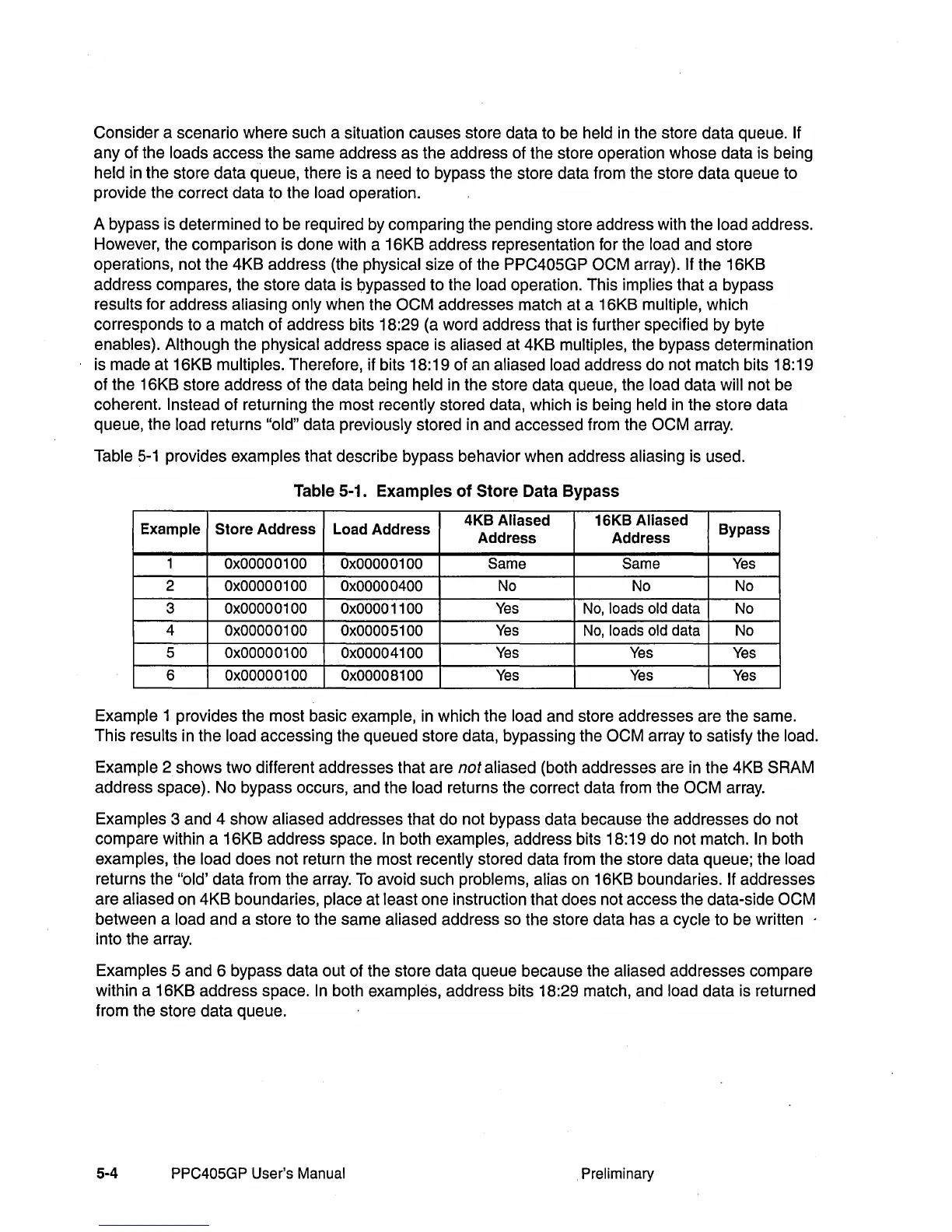

Table

5-1

provides examples that describe bypass behavior when address aliasing is used.

Table 5-1. Examples

of

Store Data Bypass

Example Store Address

Load

Address

4KB

Allased

16KB

Allased

Bypass

Address Address

1

OxOOOO0100

OxOOOO0100

Same Same

Yes

2

OxOOOO0100

OxOOOO0400

No No No

3

OxOOOO0100

OxOOO01100

Yes

No,

loads

old

data

No

4

OxOOOO0100

Ox00005100

Yes

No,

loads

old

data

No

5

OxOOOO0100

Ox000041

00

Yes

Yes

Yes

6

OxOOOO0100

Ox000081

00

Yes

Yes

Yes

Example 1 provides the most basic example,

in

which the load and store addresses are the same.

This results in the

load accessing the queued store data, bypassing the OCM array to satisfy the load.

Example 2 shows two different addresses that are

not

aliased (both addresses are

in

the 4KB SRAM

address space). No bypass occurs, and the

load returns the correct data from the OCM array.

Examples 3 and 4 show aliased addresses that do not bypass data because the addresses do not

compare within a 16KB address space.

In

both examples, address bits 18:19 do not match. In both

examples, the

load does not return the most recently stored data from the store data queue; the load

returns the "old' data from the array.

To

avoid such problems, alias

on

16KB boundaries. If addresses

are

aliased on 4KB boundaries, place at least one instruction that does not access the data-side OCM

between a load and a store to the same aliased address so the store data has a cycle to be written .

into the array.

Examples 5 and 6 bypass data out of the store data queue because the aliased addresses compare

within a 16KB address space.

In

both examples, address bits 18:29 match, and load data is returned

from the store data queue.

5-4

PPC405GP

User's

Manual

Preliminary

Loading...

Loading...