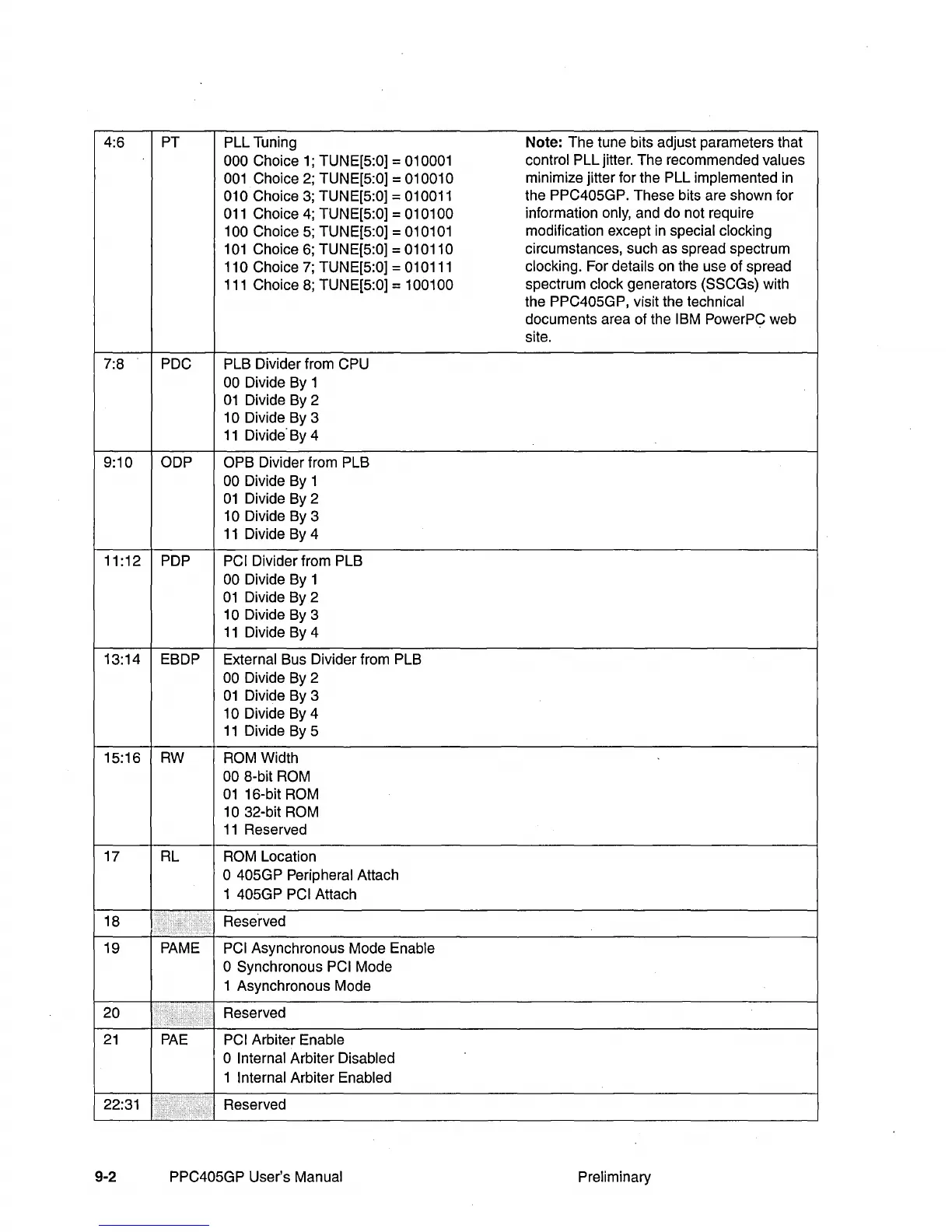

4:6 PT PLL Tuning Note: The tune bits adjust parameters that

000 Choice

1;

TUNE[5:0] = 010001

control PLL jitter. The recommended values

001

Choice 2; TUNE[5:0] = 010010

minimize jitter for the PLL implemented in

010 Choice

3;

TUNE[5:0] = 010011

the PPC405GP. These bits are shown for

011

Choice

4;

TUNE[5:0] = 010100

information only, and do not require

100 Choice

5;

TUNE[5:0] = 010101

modification except

in

special clocking

101

Choice

6;

TUNE[5:0] = 010110

circumstances, such as spread spectrum

110 Choice

7;

TUNE[5:0] = 010111

clocking. For details on the use of spread

111

Choice

8;

TUNE[5:0] = 100100

spectrum clock generators (SSCGs) with

the

PPC405GP, visit the technical

documents area of the IBM PowerPC web

site.

7:8

PDC PLB Divider from CPU

00

Divide By 1

01

Divide By 2

10 Divide By 3

11

Divide· By 4

9:10 ODP OPB Divider from PLB

00

Divide By 1

01

Divide By 2

10 Divide By 3

11

Divide By 4

11

:12 PDP PCI Divider from PLB

00

Divide By 1

01

Divide By 2

10 Divide By 3

11

Divide By 4

13:14

EBDP External Bus Divider from PLB

00

Divide By 2

01

Divide By 3

10 Divide By 4

11

Divide By 5

15:16 RW

ROM Width

00 8-bit ROM

01

16-bit ROM

10

32-bit ROM

11

Reserved

17 RL

ROM Location

o 405GP Peripheral Attach

1

405GP PCI Attach

18

..

Rese·rved

19

PAME

PCI Asynchronous Mode Enable

o Synchronous PCI Mode

1 Asynchronous Mode

20 Reserved

...

21

PAE

PCI Arbiter Enable

o Internal Arbiter Disabled

1 Internal Arbiter Enabled

22:31

I

Reserved

9-2

PPC405GP User's Manual Preliminary

Loading...

Loading...