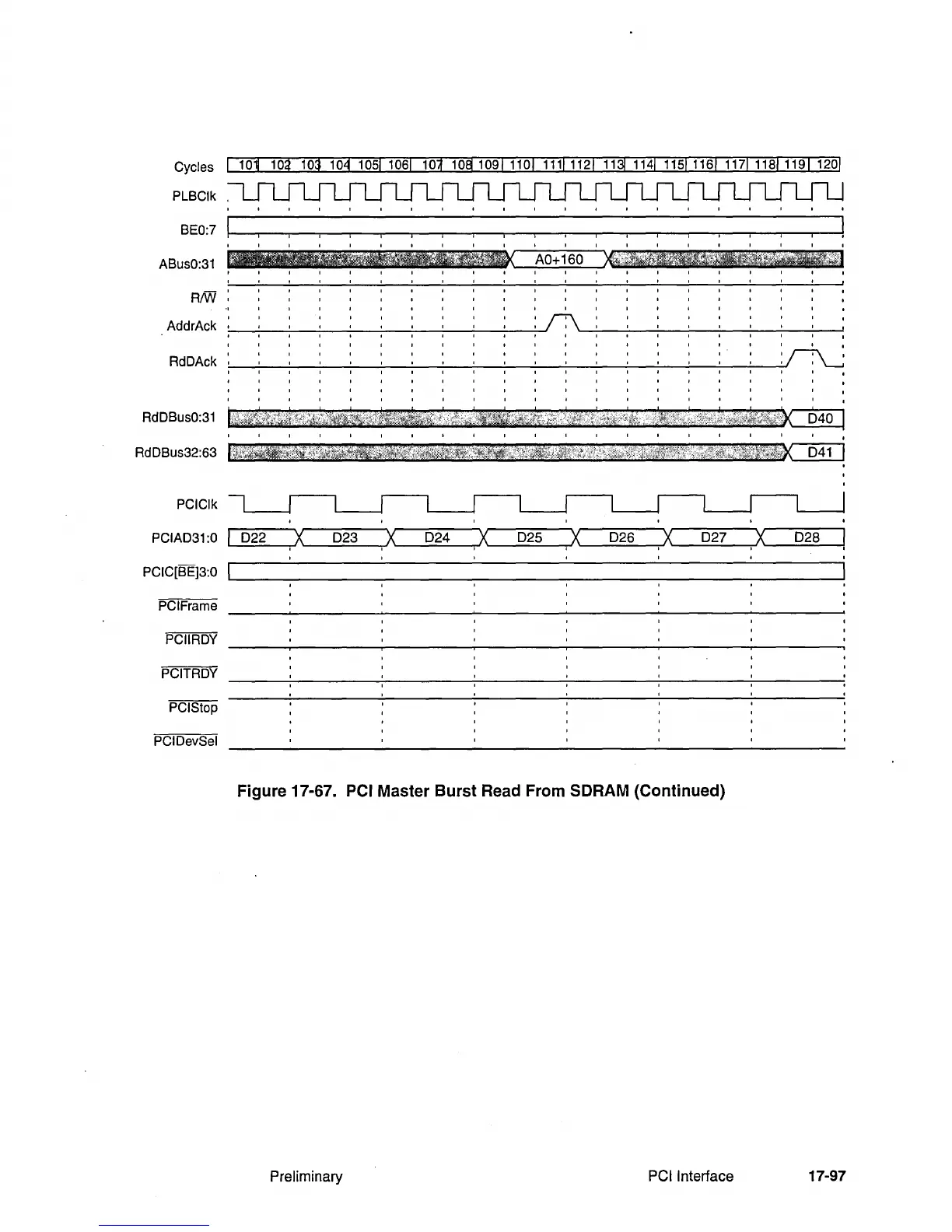

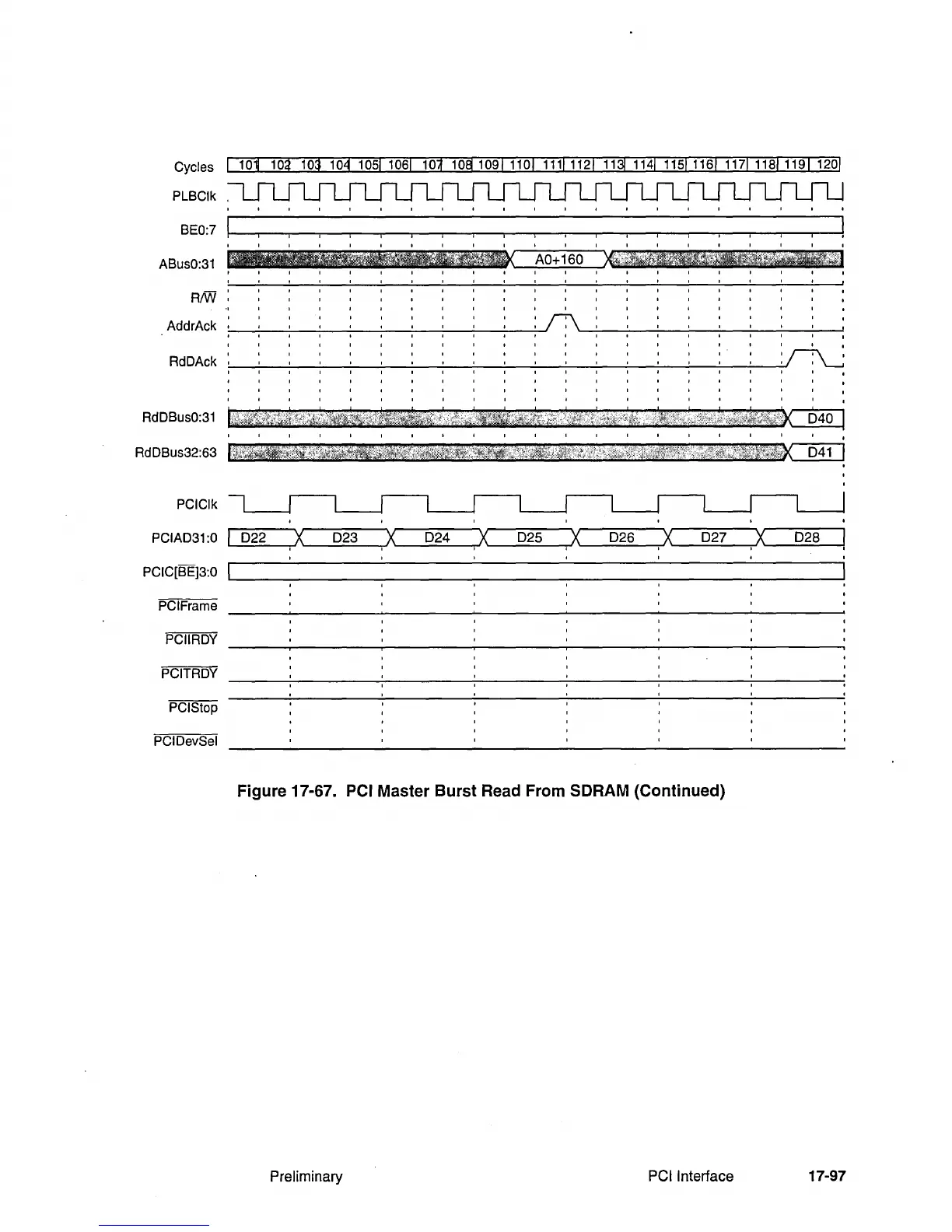

Cycles

PLBClk

BEO:?

I I I I I I I I I I I I I I I I I I

ABusO:31

~qet~'5

__

iSII?<'---:-A~o+-1:-::6~o~)(4;~Wfll"":1

__

'i~;J

AIW

,

AdDBusO:31

Wb1iti~;{·i1;ii<\!:;;il~~~;Wii'1ii#iU;,*;$v}//;I:;;i\ilt,,;jS;

&',;:h(',;tq;~:{'~t,~ii>::$;

d~;:\::;\,:c

:~!bL!i·.;yk\t;~"::i\i"~

AdDBus32:63

';ll{jjl_,k,a'';J'~Jl;Jai0.tiG:;is;in;i4fii:4::;:if:,s:4"ri\2;\};;kIz:!:i,\,;:/(,;},:<~;~>a,,,\(J>ij2¥YUYj

:,:;\::'Kif<~i<t'\!j:f;;4;~

PCIClk

PCIAD31:0

D22 X

023

X

024

X

025

X

026

X

027

X

028

PCIC[BE]3:0

PCIFrame

PCIDevSel

Figure 17-67. PCI Master Burst Read From SDRAM (Continued)

Preliminary PCI Interface

17-97

Loading...

Loading...