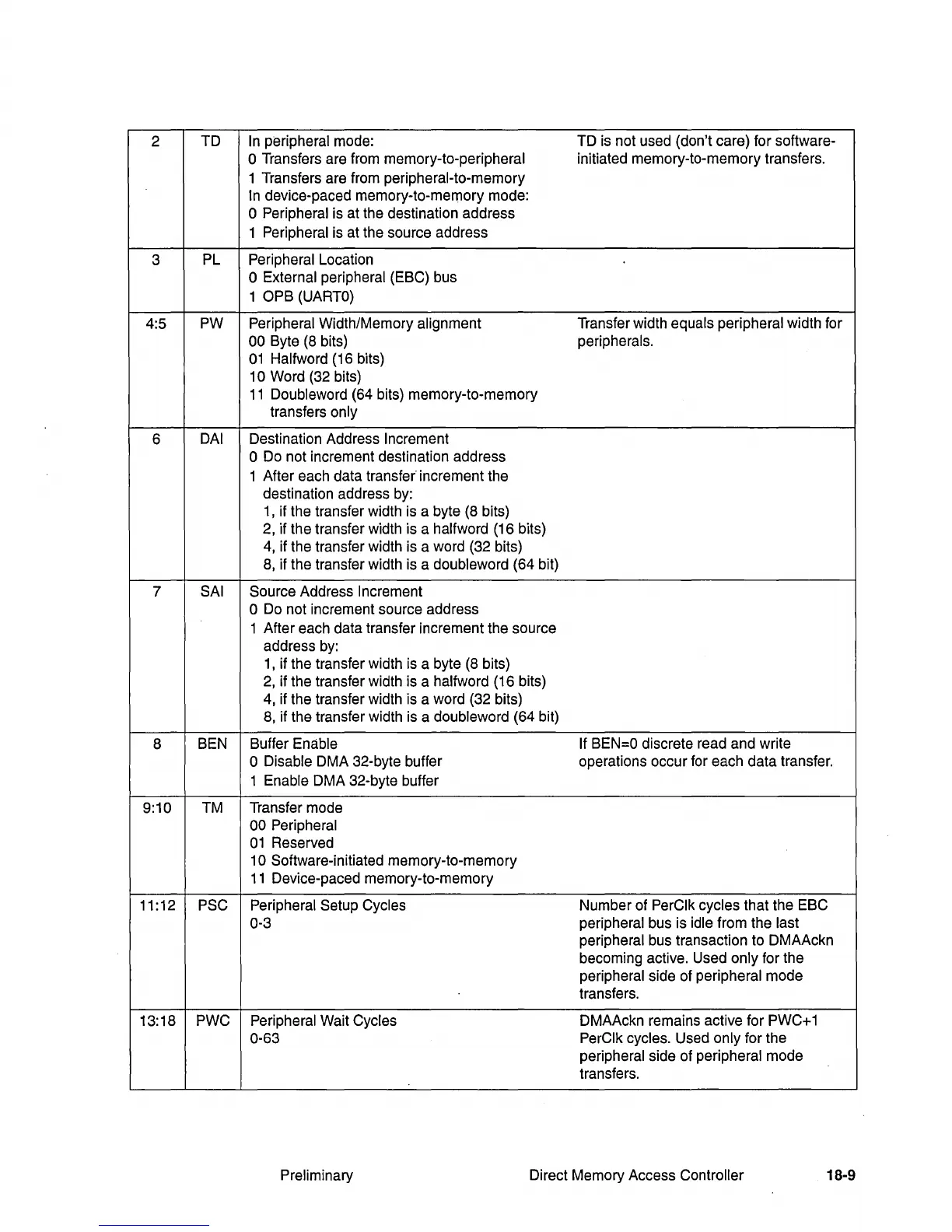

2

TD

In

peripheral mode:

TD is not used (don't care) for software-

o Transfers are from memory-to-peripheral initiated memory-to-memory transfers.

1 Transfers are from peripheral-to-memory

In

device-paced memory-to-memory mode:

o Peripheral is at the destination address

1

Peripheral is at the source address

3

PL Peripheral Location

o External peripheral (EBC) bus

1

OPB

(UARTO)

4:5

PW Peripheral Width/Memory alignment

Transfer width equals peripheral width for

00 Byte

(8

bits) peripherals.

01

Halfword (16 bits)

10 Word (32 bits)

11

Doubleword (64 bits) memory-to-memory

transfers

only

6

DAI

Destination Address Increment

o Do not increment destination address

1 After each data transfer' increment the

destination address

by:

1,

if the transfer width is a byte (8 bits)

2, if the transfer width is a

halfword (16 bits)

4,

if the transfer width is a word (32 bits)

8,

if the transfer width is a doubleword (64 bit)

7 SAl Source Address Increment

o Do not increment source address

1 After each data transfer increment the source

address

by:

1,

if the transfer width is a byte

(8

bits)

2,

if the transfer width is a halfword (16 bits)

4, if the transfer width is a word (32 bits)

8,

if the transfer width is a doubleword (64 bit)

8

BEN Buffer

Enable

If

BEN=O

discrete read and write

o Disable DMA 32-byte buffer

operations occur for each data transfer.

1

Enable DMA 32-byte buffer

9:10 TM

Transfer mode

00 Peripheral

01

Reserved

10 Software-initiated memory-to-memory

11

Device-paced memory-to-memory

11

:12

PSC

Peripheral Setup Cycles Number of PerClk cycles that the EBC

0-3

peripheral bus is idle from the last

peripheral

bus transaction to DMAAckn

becoming active. Used

only for the

peripheral side of peripheral mode

transfers.

13:18

PWC

Peripheral Wait Cycles DMAAckn remains active for PWC+ 1

0-63 PerClk cycles. Used only for the

peripheral side of peripheral mode

transfers.

Preliminary Direct Memory Access Controller 18-9

Loading...

Loading...