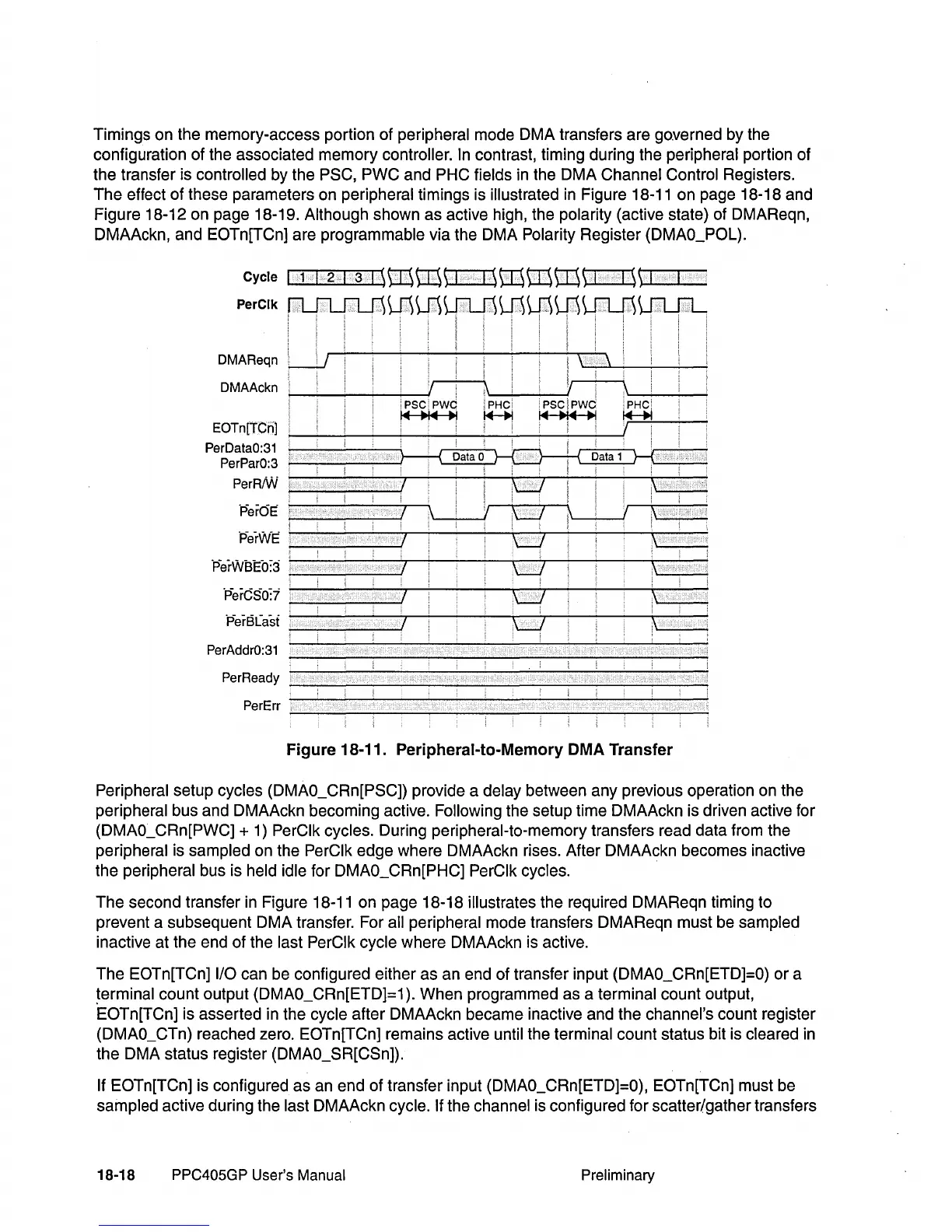

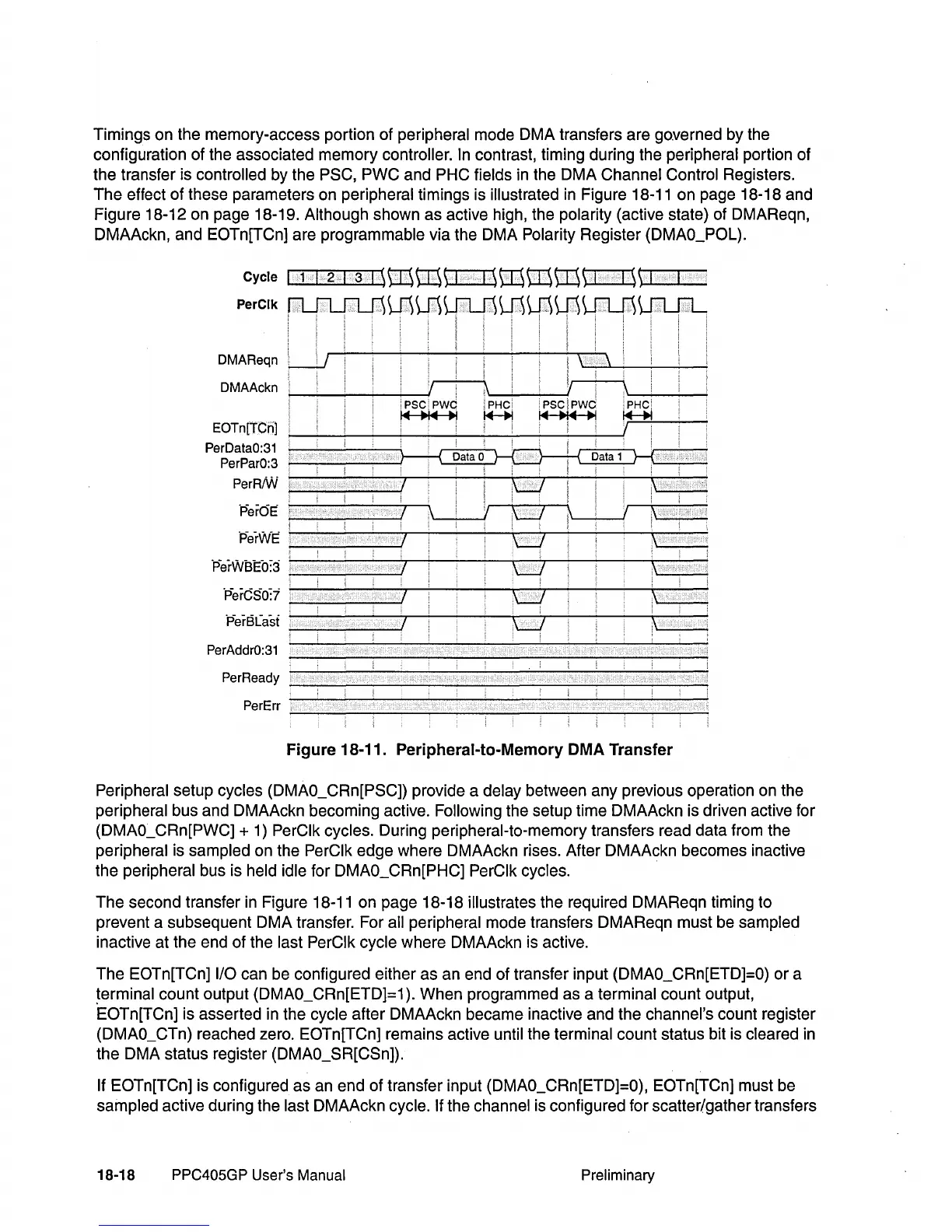

Timings on the memory-access portion of peripheral mode DMA transfers are governed by the

configuration of the associated memory

controller.

In

contrast, timing during the peripheral portion of

the transfer is

controlled by the PSC, PWC and PHC fields

in

the DMA Channel Control Registers.

The effect of these parameters on

peripheral timings is illustrated

in

Figure 18-11 on page 18-18 and

Figure 18-12 on page 18-19.

Although shown as active high, the polarity (active state) of DMAReqn,

DMAAckn, and

EOTn[TCn] are programmable via the DMA Polarity Register (DMAO_POL).

Cycle 1 1

12131

)tIStISo=ntIStIStISo=n~)-.J...I--L-

PerClk

n.rLJlJ")

Lf)

W1

WlJ1

Lf) Lf)

~

~

Wl.fL

EOTn[TCril

PerDataO:31

PerParO:3

~-"---";';""/

i

PerRNJ

_~~~---{

·PerDE

:==:':':'-:"-:"-=--...J~--i;'---.J

C~

LLJ...----r-c=J--'-;"

•.

-.

.....;;

P~WE

~--~~--r~~--~~.t=J-.

~·'-----:--~ic=J-··--·~··

.

·PerWBECJ:3

'--..,..._..,..._..,..._---11

'C.J

c=J

·PereS-o:?

~

__

~---I

CJ

c=J

·PerBLasi

______

-..,..._---11

CJ

c=J

PerAddrO:31

PerReady

_____

_"

___

~_:_:-...,.__---"-"--

PerErr

-"_-..;.;

______

-..;.;

___________

~_"

Figure 18-11. Peripheral-to-Memory DMA Transfer

Peripheral setup cycles (DMAO_CRn[PSC]) provide a delay between any previous operation on the

peripheral bus and DMAAckn becoming active. Following the setup time DMAAckn is driven active for

(DMAO_CRn[PWC]

+ 1) PerClk cycles. During peripheral-to-memory transfers read data from the

peripheral is sampled on the PerClk edge where DMAAckn rises. After DMAAckn becomes inactive

the

peripheral bus is held idle for DMAO_CRn[PHC] PerClk cycles.

The second transfer

in

Figure 18-11 on page 18-18 illustrates the required DMAReqn timing to

prevent a subsequent DMA transfer. For

all peripheral mode transfers DMAReqn must be sampled

inactive at the end of the last PerClk cycle where DMAAckn is active.

The EOTn[TCn]

1/0

can be configured either as an end of transfer input (DMAO_CRn[ETD]=O) or a

~erminal

count output (DMAO_CRn[ETD]=1). When programmed as a terminal count output,

EOTn[TCn] is asserted in the cycle after DMAAckn became inactive and the channel's count register

(DMAO_CTn) reached zero.

EOTn[TCn] remains active until the terminal count status bit is cleared

in

the DMA status register (DMAO_SR[CSn]).

If EOTn[TCn]

is configured as an end of transfer input (DMAO_CRn[ETD]=O), EOTn[TCn] must be

sampled active during the last DMAAckn cycle. If the channel is configured for scatter/gather transfers

18-18

PPC405GP User's Manual Preliminary

Loading...

Loading...