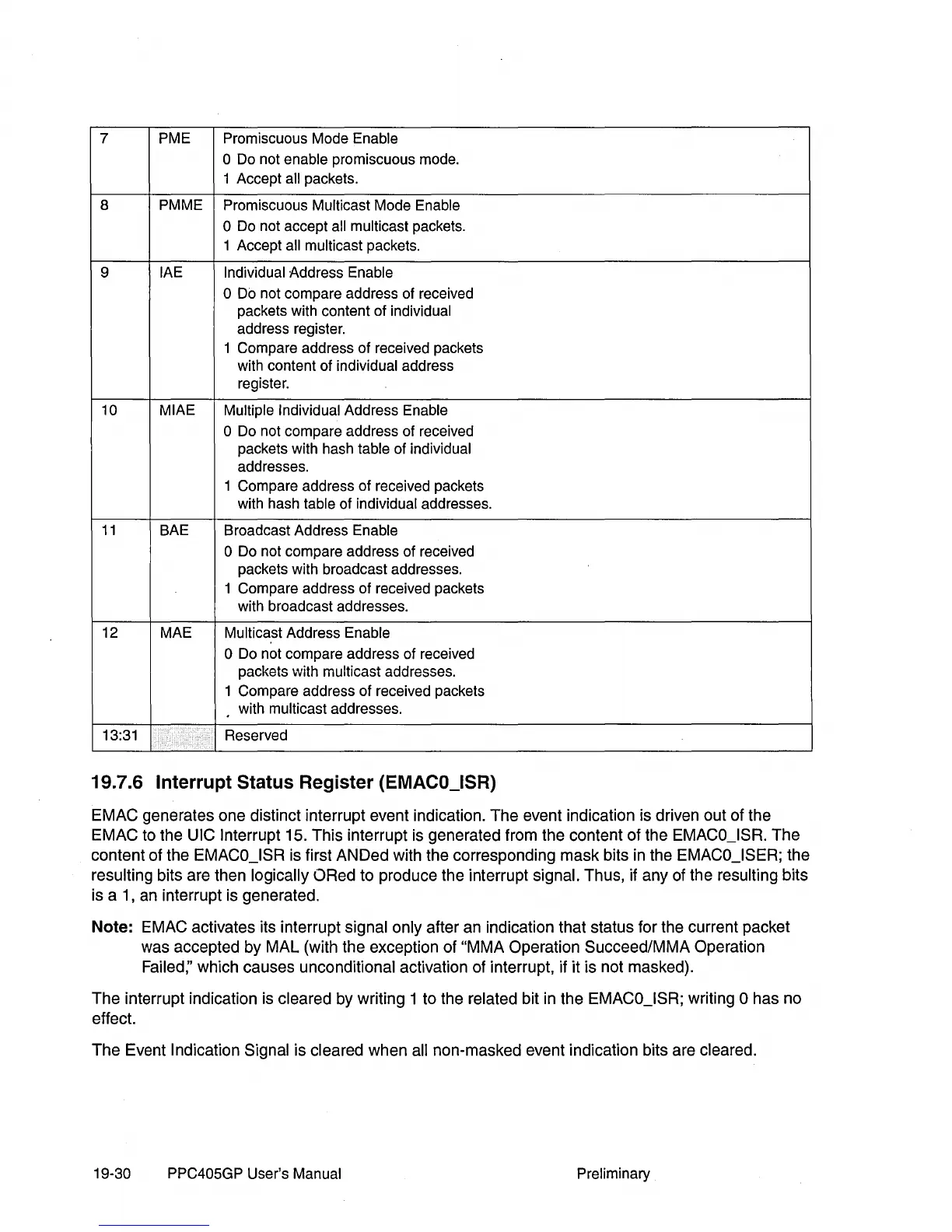

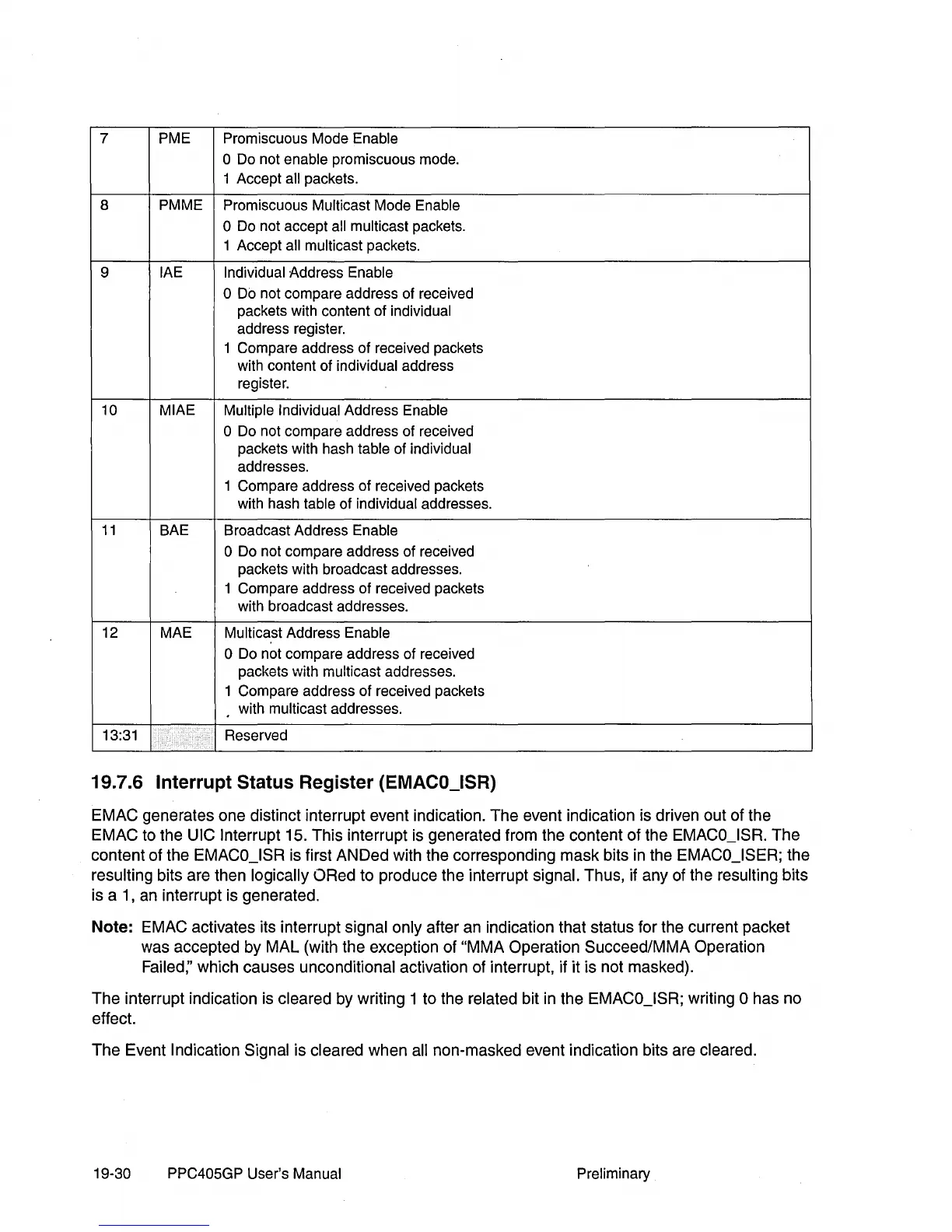

7 PME Promiscuous Mode Enable

o Do not enable promiscuous mode.

1 Accept all packets.

8 PMME

Promiscuous

Multicast Mode Enable

o Do not accept all multicast packets.

1 Accept all multicast packets.

9

IAE

Individual Address Enable

o Do not compare address of received

packets with content of individual

address register.

1 Compare address of received packets

with content of individual address

register.

10

MIAE

Multiple Individual Address Enable

o Do not compare address of received

packets with hash table of individual

addresses.

1 Compare address of received packets

with hash table of individual addresses.

11

BAE

Broadcast Address Enable

o Do not compare address of received

packets with broadcast addresses.

1 Compare address of received packets

with broadcast addresses.

12 MAE

Multicast Address Enable

o Do not compare address of received

packets with multicast addresses.

1 Compare address of received packets

with multicast addresses.

13:31 Reserved

19.7.6 Interrupt Status Register (EMACO_ISR)

EMAC generates one distinct interrupt event indication. The event indication is driven out of the

EMAC to the

UIC Interrupt 15. This interrupt is generated from the content of the EMACO_ISR. The

content of the

EMACO_ISR is first ANOed with the corresponding mask bits

in

the EMACO_ISER; the

resulting bits are then logically

ORed to produce the interrupt signal. Thus, if any of the resulting bits

is a

1,

an interrupt is generated.

Note: EMAC activates its interrupt signal only after an indication that status for the current packet

was accepted by MAL (with the exception of

"MMA Operation Succeed/MMA Operation

Failed:' which causes unconditional activation of interrupt, if it is not masked).

The interrupt indication is cleared by writing 1 to the related bit

in

the EMACO_ISR; writing ° has no

effect.

The Event

Indication Signal is cleared when all non-masked event indication bits are cleared.

19-30

PPC405GP User's Manual Preliminary

Loading...

Loading...