28

TE1

Transmit Error 1 EMAC aborts the transmitted packet if one

o TX Channel 1 transmission OK

of the following events takes place:

1

TX

Channel 1 transmission aborted

• Late collision detection

• Excessive collision detection

• Excessive deferral

• TX FIFO underrun

• Loss of carrier sense

29

Reserved Always

0

30 MOS

MMA Operation Succeeded

The device driver should poll assertion of

o MMA_CONTROL addressed on the OPB

EMACO_ISR[MOS]

or EMACO_ISR[MOF]

1 PHY transfer valid

before issuing a new command or before

using data read from the

PHY.

31

MOF MMA Operation Failed The device driver should poll assertion of

o MMA_CONTROL addressed on the OPB

EMACO_ISR[MOF]

or EMACO_ISR[MOS]

1 PHY transfer

not

valid

before issuing a new command or before

using data read from the

PHY.

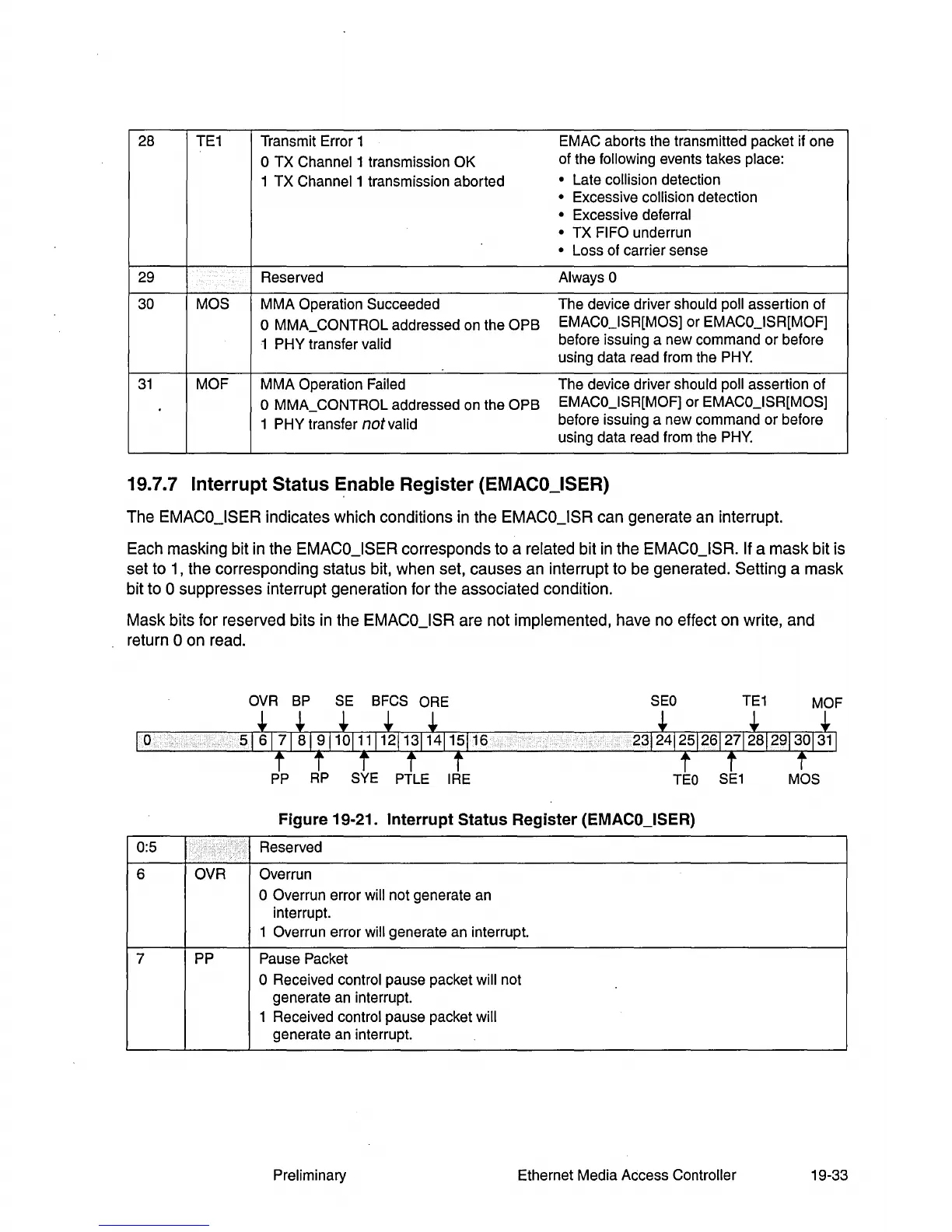

19.7.7 Interrupt Status

~nable

Register (EMACO_ISER)

The EMACO_ISER indicates which conditions

in

the EMACO_ISR can generate an interrupt.

Each masking bit in the

EMACO_ISER corresponds to a related bit

in

the EMACO_ISR. If a mask bit is

set to

1,

the corresponding status bit, when set, causes an interrupt to be generated. Setting a mask

bit to

° suppresses interrupt generation for the associated condition.

Mask bits for reserved bits

in

the EMACO_ISR are not implemented, have no effect on write, and

return

° on read.

OVR

BP

SE

BFCS

ORE

SE~

TE1

MOF

PP

RP

SYE

PTLE

IRE

TEO

SE1

MaS

Figure 19·21. Interrupt Status Register (EMACO_ISER)

0:5

..

Reserved

.,

6 OVR Overrun

o Overrun error will not generate an

interrupt.

1

Overrun error will generate an interrupt.

7 PP Pause Packet

o Received control pause packet will not

generate an interrupt.

1 Received control pause packet will

generate an interrupt.

Preliminary Ethernet Media Access Controller 19-33

Loading...

Loading...