25

TEO

Transmit Error 0

.

o TX error on TX Channel 0 will not

generate an interrupt.

1 TX error on TX Channel

0 will generate

an interrupt.

26

Reserved

27

SE1

SQE Error 1

o SQE error on TX Channel 1 will not

generate an interrupt.

1

SQE error on TX Channel 1 will generate

an interrupt.

28

TE1

Transmit Error 1

.

o TX error on TX Channel 1 will not

generate an interrupt.

1 TX error on TX Channel 1 will generate

an interrupt.

29

Reserved

30

MOS

MMA Operation Succeeded

o Successful MMA Operation with a PHY

will not generate an interrupt.

1 Successful MMA Operation with a

PHY

will

generate an interrupt.

31

MOF MMA Operation Failed

o Unsuccessful MMA Operation with a

PHY will not generate an interrupt.

1 Unsuccessful MMA Operation with a

PHY will generate an interrupt.

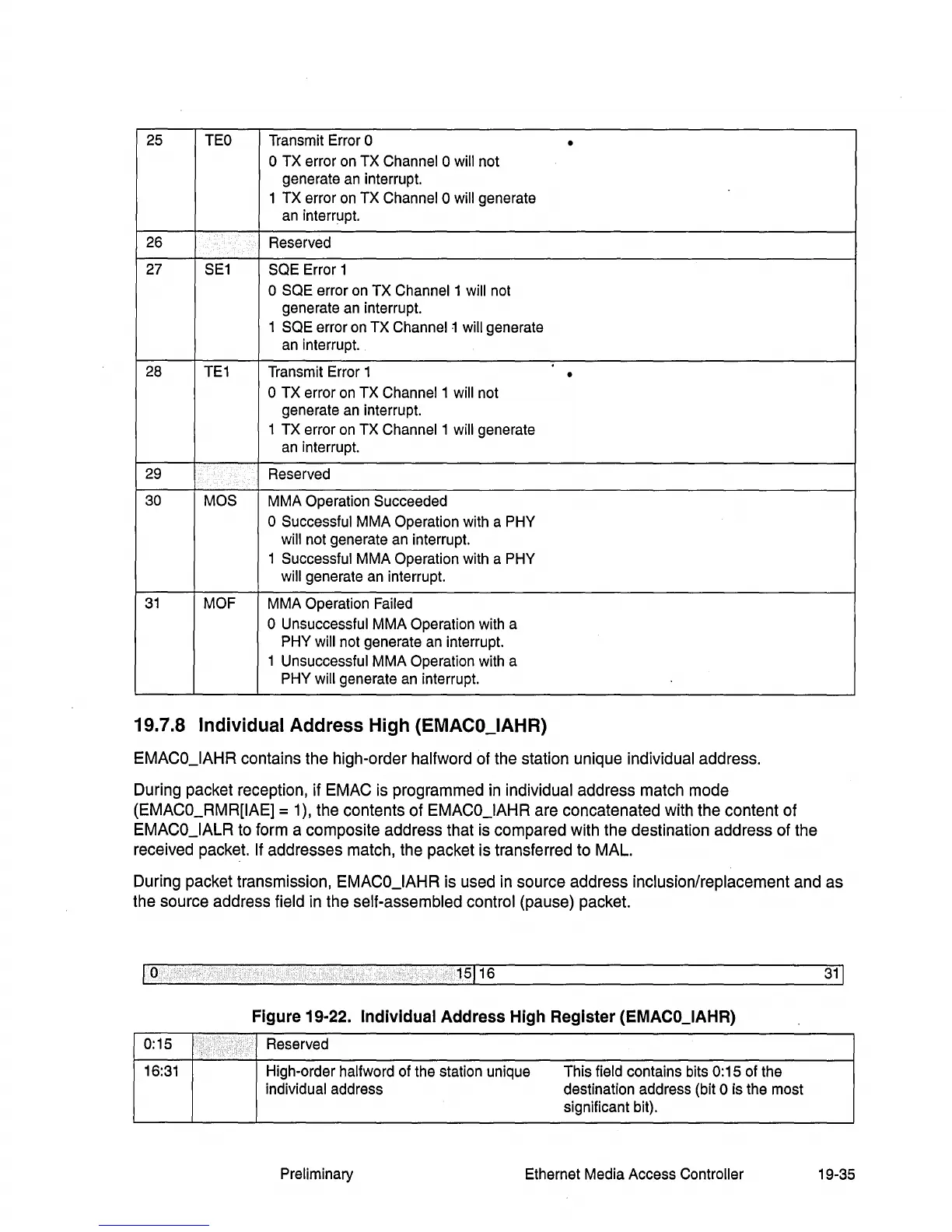

19.7.8 Individual Address High (EMACO_IAHR)

EMACO_IAHR

contains

the

high-order halfword

of

the

station

unique

individual address.

During

packet

reception,

if

EMAC

is

programmed

in

individual address

match

mode

(EMACO_RMR[IAE]

=

1),

the

contents

of

EMACO_IAHR

are

concatenated

with

the

content

of

EMACO_IALR

to

form

a composite address that

is

compared

with

the

destination address

of

the

received

packet.

If

addresses

match,

the

packet

is

transferred

to

MAL.

During

packet

transmission,

EMACO_IAHR

is

used

in

source address inclusion/replacement

and

as

the

source

address

field

in

the

self-assembled control

(pause)

packet.

10

151

16

Figure 19·22. Individual Address High Register (EMACO_IAHR)

0:15

Reserved

,

'.

16:31

High-order halfword of the station unique This field contains bits 0:15 of the

individual address destination address (bit

0 is the most

significant bit).

Preliminary

Ethernet Media Access Controller 19-35

Loading...

Loading...