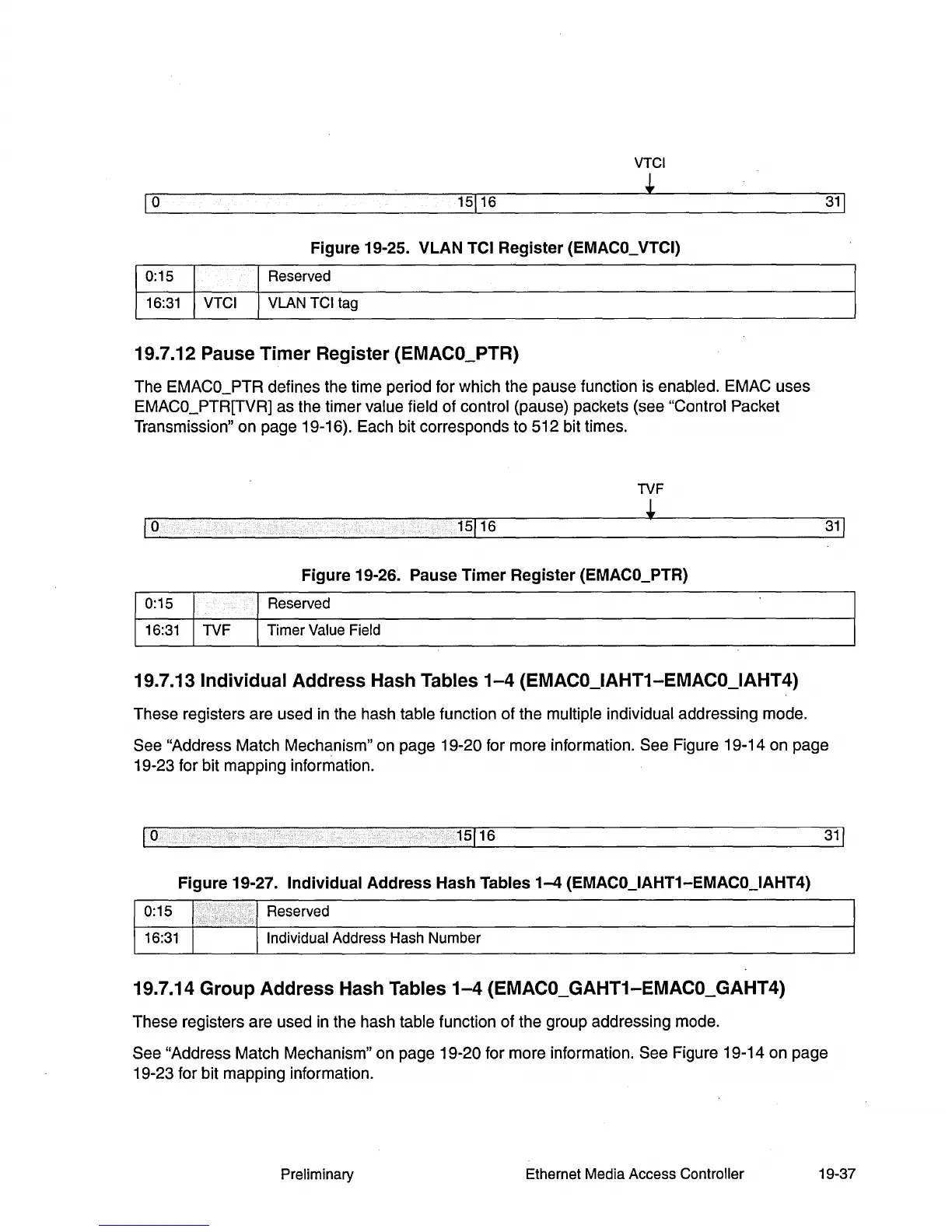

VTCI

15

1

16

*

Figure 19-25. VLAN TCI Register (EMACO_ VTCI)

I

0'15 I I Reserved

1

~:31

VTCI VLAN TCI tag

19.7.12 Pause Timer Register (EMACO_PTR)

The EMACO_PTR defines the time period for which the pause function is enabled. EMAC uses

EMACO_PTR[TVR] as the timer

value field of control (pause) packets (see "Control Packet

Transmission" on page 19-16). Each bit corresponds to 512 bit times.

TVF

1

0

15

1

16

*

Figure 19-26. Pause Timer Register (EMACO_PTR)

I

0'15 I I Reserved

1

~:31

TVF Timer Value Field

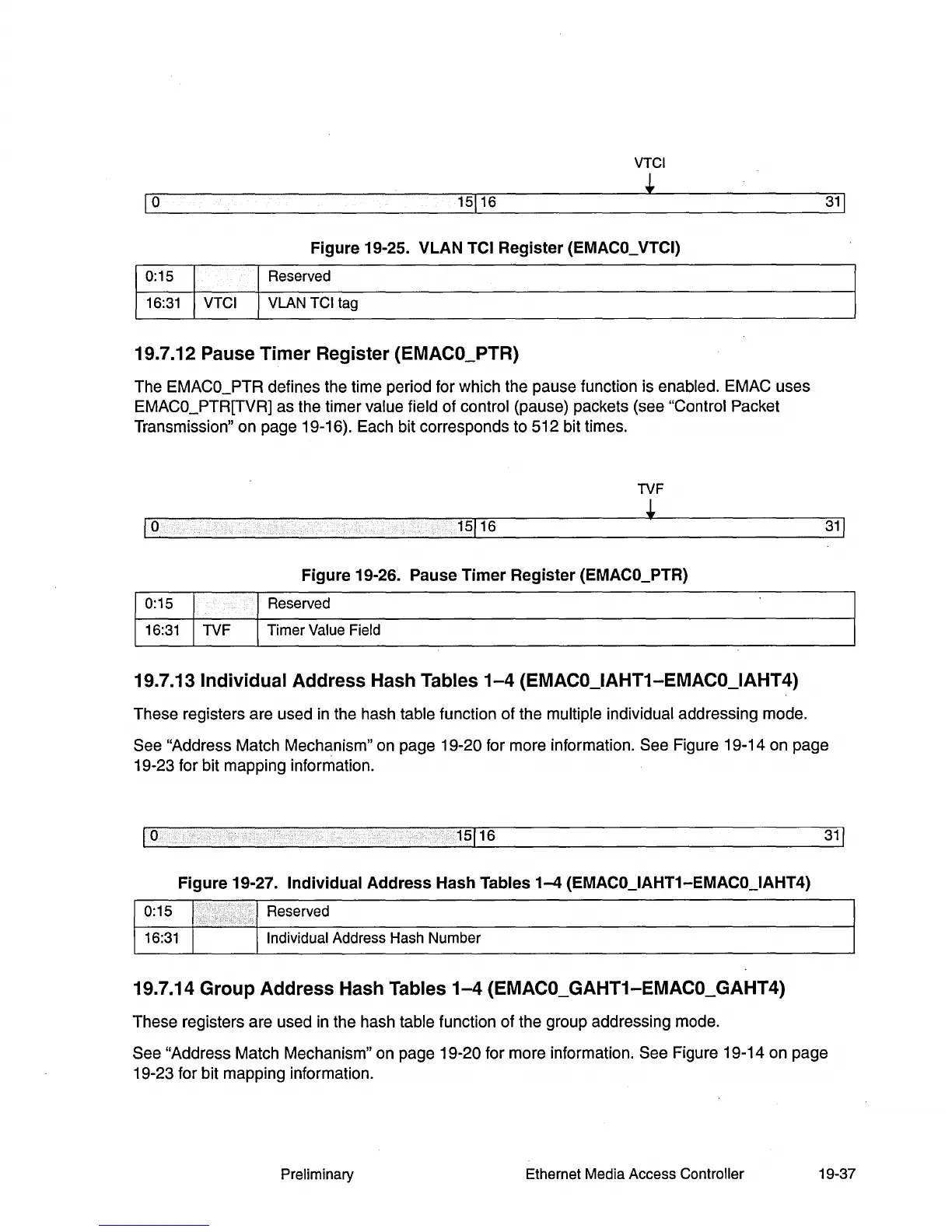

19.7.13 Individual Address Hash Tables

1-4

(EMACO_IAHT1-EMACO_IAHT4)

31

1

These registers are used in the hash table function of the multiple individual addressing mode.

See

"Address Match Mechanism" on page 19-20 for more information. See Figure 19-14 on page

19-23 for bit mapping information.

1

0 15

1

16

31

1

Figure 19-27. Individual Address Hash Tables

1-4

(EMACO_IAHT1-EMACO_IAHT4)

Reserved

Individual Address Hash Number

19.7.14 Group Address Hash Tables

1-4

(EMACO_GAHT1-EMACO_GAHT4)

These registers are used

in

the hash table function of the group addressing mode.

See

"Address Match Mechanism" on page 19-20 for more information. See Figure 19-14 on page

19-23 for bit mapping information.

Preliminary

Ethernet Media Access Controller 19-37

Loading...

Loading...