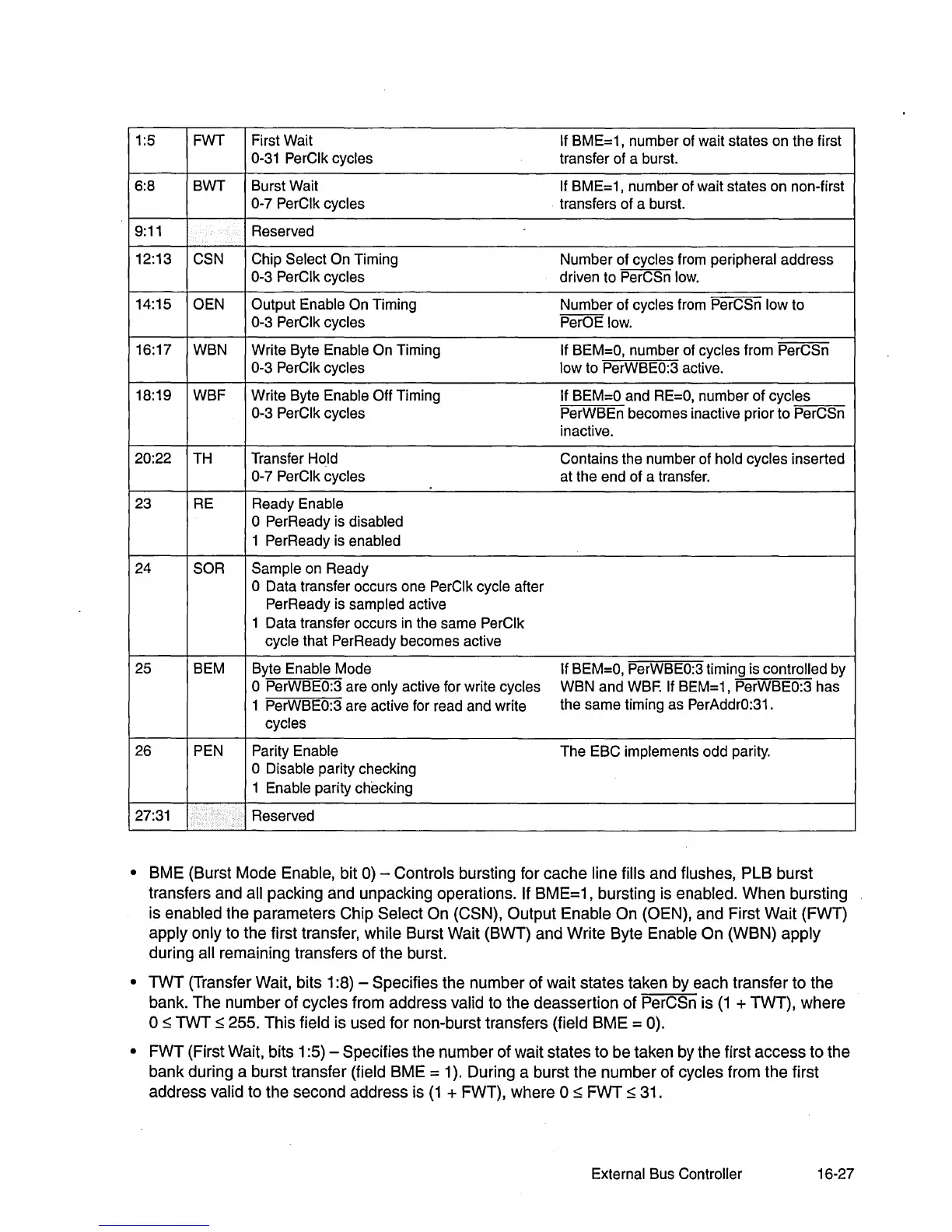

1:5

FWT First Wait

If BME=1, number of wait states on the first

0-31

PerClk cycles

transfer of a burst.

6:8 BWT Burst Wait

If BME=1, number of wait states on non-first

0-7 PerClk cycles transfers of a burst.

9:11 Reserved

12:13 CSN

Chip Select

On Timing

Number of cycles from peripheral address

0-3 PerClk cycles

driven to PerCSn low.

14:15

OEN Output Enable On Timing

Number of cycles from PerCSn low to

0-3 PerClk cycles

PerOE low.

16:17

WBN Write Byte Enable

On Timing

If BEM=O, number of cycles from PerCSn

0-3 PerClk cycles

low to PerWBEO:3 active.

18:19

WBF Write Byte Enable

Off Timing

If BEM=O and

RE=O,

number of cycles

0-3 PerClk cycles

PerWBEn becomes inactive prior to PerCSn

inactive.

20:22 TH

Transfer Hold Contains the number of hold cycles inserted

0-7 PerClk cycles

at the end of a transfer.

23

RE Ready Enable

o PerReady is disabled

1 PerReady is enabled

24

SOR Sample on Ready

o Data transfer occurs one PerClk cycle after

PerReady is sampled active

1 Data transfer occurs

in

the same PerClk

cycle that PerReady becomes active

25 BEM Byte Enable Mode

If BEM=O, PerWBEO:3 timing is controlled by

o PerWBEO:3 are only active for write cycles

WBN and

WBF.

If BEM=1, PerWBEO:3 has

1 PerWBEO:3 are active for read and write

the same timing as PerAddrO:31.

cycles

26

PEN Parity Enable

The EBC implements odd parity.

o Disable parity checking

1 Enable parity checking

27:31

Reserved

• BME (Burst Mode Enable, bit 0) - Controls bursting for cache line fills and flushes, PLB burst

transfers and

all packing and unpacking operations. If BME=1, bursting is enabled. When bursting

is

enabled the parameters Chip Select On (CSN), Output Enable On (OEN), and First Wait (FWT)

apply only to the first transfer, while Burst Wait (BWT) and Write Byte Enable On (WBN) apply

during all remaining transfers of the burst.

•

TWT

(Transfer Wait, bits 1 :8) - Specifies the number of wait states taken by each transfer to the

bank. The number of

cycles from address valid to the deassertion of PerCSn is

(1

+ TWT), where

o

:s;

TWT

:s;

255. This field is used for non-burst transfers (field BME = 0).

•

FWT (First Wait, bits 1 :5) - Specifies the number of wait states to be taken by the first access to the

bank during a burst transfer

(field BME = 1). During a burst the number of cycles from the first

address

valid to the second address is

(1

+ FWT), where

O:S;

FWT:S;

31.

External Bus Controller 16-27

Loading...

Loading...