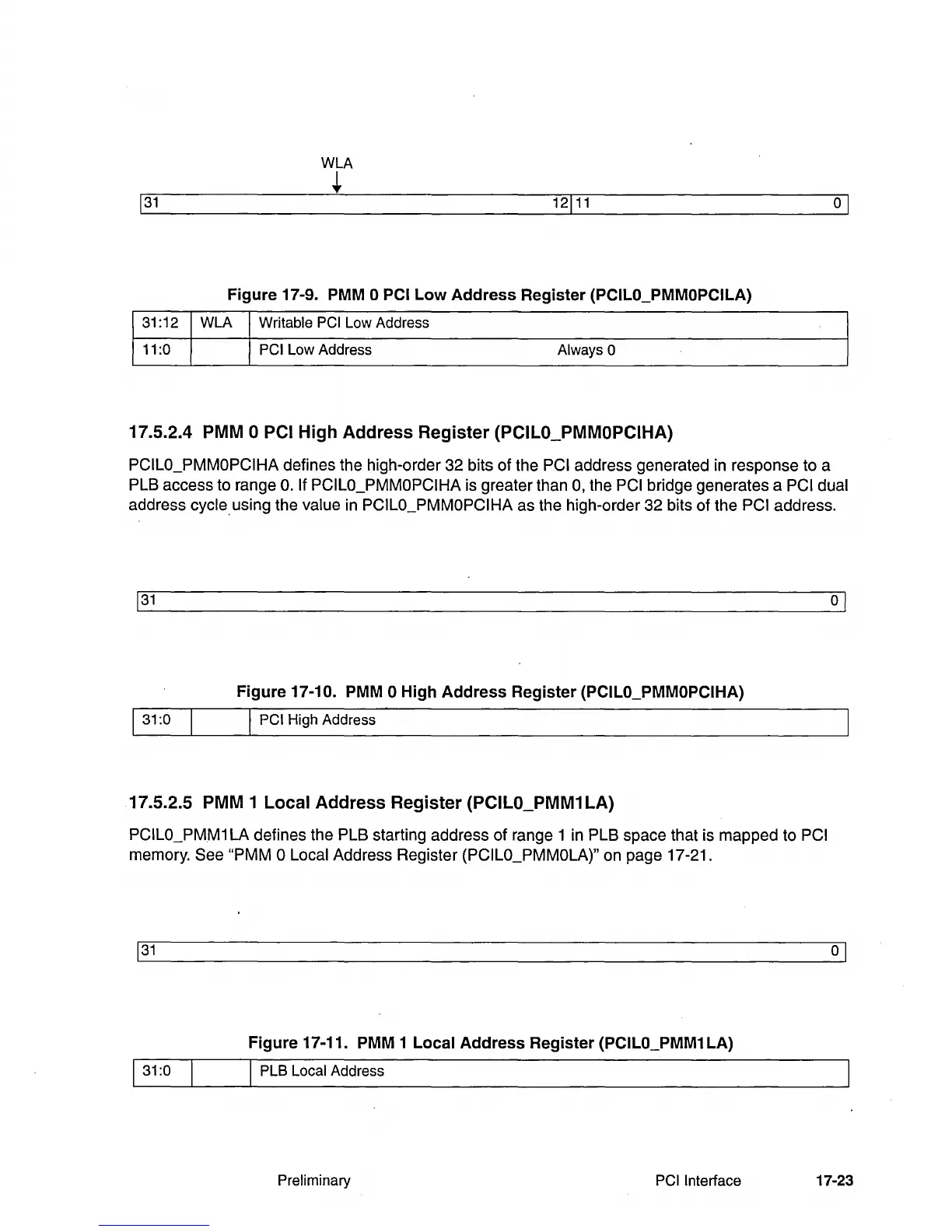

WLA

~

12111

01

Figure 17-9.

PMM

0 PCI

Low

Address

Register (PCILO_PMMOPCILA)

I

31

:12

WLA

I Writable PCI Low Address

111

:0

I PCI Low Address

Always

0

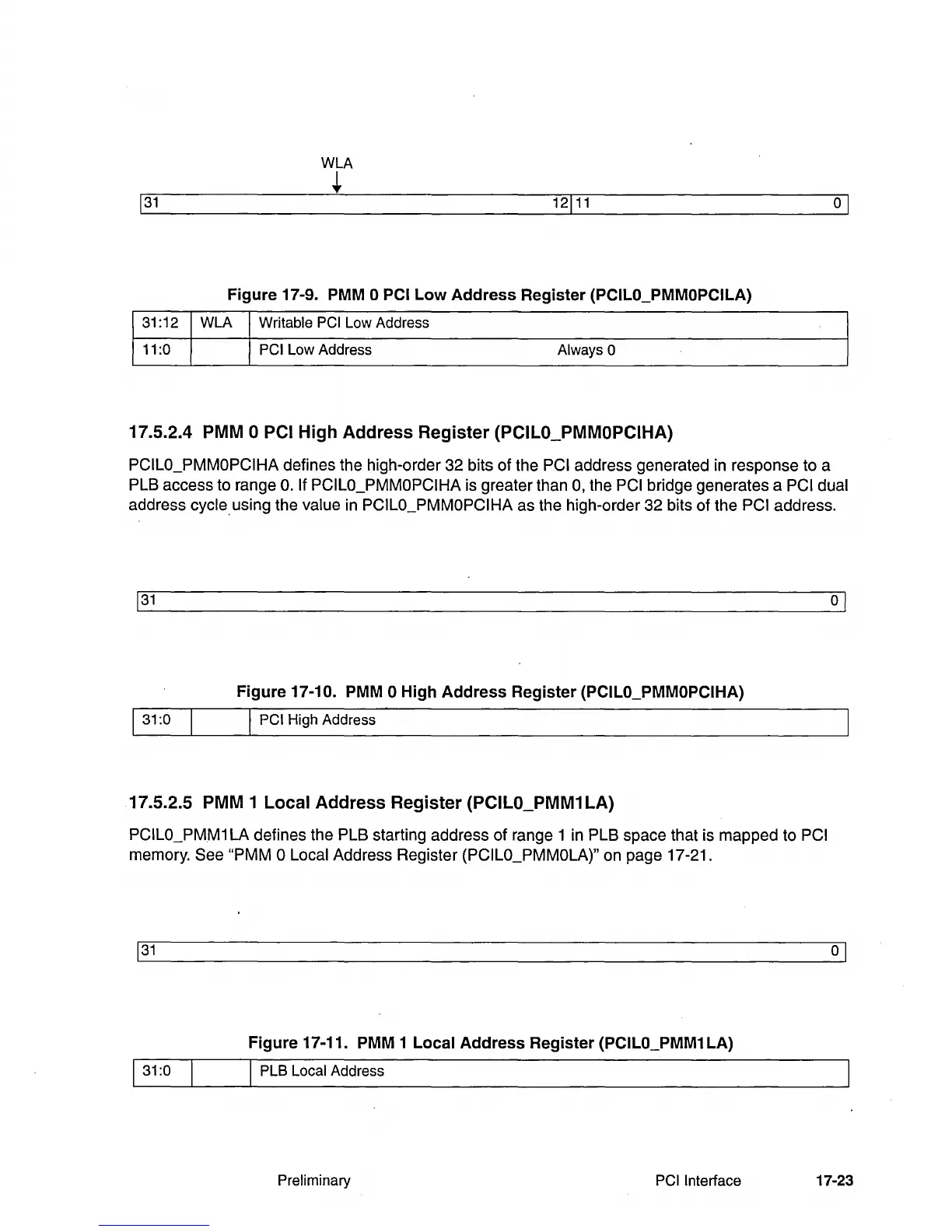

17.5.2.4

PMM

0 PCI High Address Register (PCILO_PMMOPCIHA)

PCILO_PMMOPCIHA defines the high-order 32 bits

of

the PCI address generated in response to a

PLB access to range

O.

If PCILO_PMMOPCIHA is greater than

0,

the PCI bridge generates a PCI dual

address cycle, using the value in PCILO_PMMOPCIHA as the high-order 32 bits of the PCI address.

Figure 17-10. PMM 0 High

Address

Register (PCILO_PMMOPCIHA)

I 31:0 I PCI High Address

17.5.2.5 PMM 1 Local Address Register (PCILO_PMM1 LA)

PCILO_PMM1 LA defines the PLB starting address

of

range 1 in PLB space that is mapped to PCI

memory. See "PMM 0 Local Address Register (PCILO_PMMOLA)" on page 17-21.

Figure 17-11.

PMM

1 Local

Address

Register (PCILO_PMM1 LA)

I 31:0 I PLB Local Address

01

Preliminary

PCI Interface

17-23

Loading...

Loading...