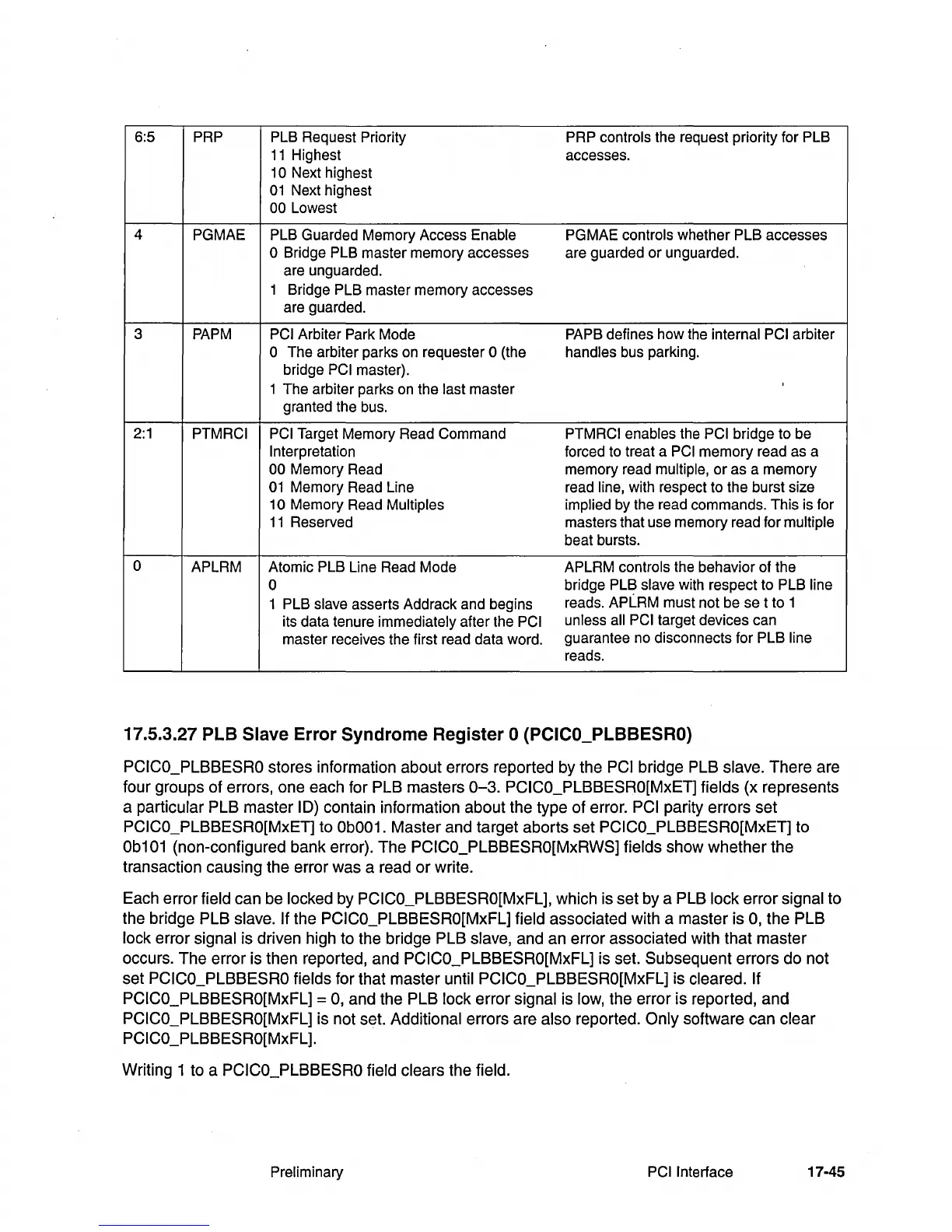

6:5

PRP PLB Request Priority PRP

controls the request priority for PLB

11

Highest accesses.

10 Next highest

01

Next highest

00 Lowest

4 PGMAE

PLB Guarded Memory Access

Enable

PGMAE controls whether PLB accesses

o Bridge PLB master memory accesses are guarded

or

unguarded.

are unguarded.

1 Bridge PLB master memory accesses

are guarded.

3

PAPM PCI Arbiter Park Mode

PAPB defines

how

the internal PCI arbiter

o The arbiter parks on requester 0 (the handles bus parking.

bridge

PCI master).

1 The arbiter parks on the

last master

granted the bus.

2:1

PTMRCI PCI Target Memory Read Command PTMRCI enables the PCI bridge to be

Interpretation forced to treat a

PCI

memory

read as a

00 Memory Read memory read multiple,

or

as

a

memory

01

Memory Read Line read line, with respect to the burst size

10 Memory Read Multiples implied by the read commands. This is for

11

Reserved masters that use memory read for multiple

beat bursts.

0

APLRM Atomic PLB Line Read Mode

APLRM

controls the behavior of the

0

bridge PLB slave with respect to PLB line

1 PLB slave asserts Addrack and begins

reads.

APLRM must

not

be se t to 1

its data tenure

immediately after the PCI

unless all PCI

target devices can

master receives the first read data word.

guarantee no disconnects for PLB

line

reads.

17.5.3.27 PLB Slave Error

Syndrome

Register 0 (PCICO_PLBBESRO)

PCICO_PLBBESRO stores information about errors reported by the PCI bridge PLB slave. There are

four groups of errors, one each for

PLB masters

0-3.

PCICO_PLBBESRO[MxET] fields (x represents

a

particular PLB master ID) contain information about the type of error. PCI parity errors set

PCICO_PLBBESRO[MxET] to Ob001. Master and target aborts set PCICO_PLBBESRO[MxET] to

Ob101

(non-configured bank error). The PCICO_PLBBESRO[MxRWS] fields show whether the

transaction causing the error was a read

or

write.

Each error

field can be locked by PCICO_PLBBESRO[MxFL], which is set by a PLB lock error signal to

the bridge

PLB slave. If the PCICO_PLBBESRO[MxFL] field associated with a master is 0, the PLB

lock

error signal is driven high to the bridge PLB slave, and an error associated with that master

occurs. The error is then reported, and

PCICO_PLBBESRO[MxFL] is set. Subsequent errors do not

set

PCICO_PLBBESRO fields for that master until PCICO_PLBBESRO[MxFL] is cleared. If

PCICO_PLBBESRO[MxFL]

= 0, and the PLB lock error Signal is low, the error is reported, and

PCICO_PLBBESRO[MxFL] is not set. Additional errors are also reported. Only software can clear

PCICO_PLBBESRO[MxFL].

Writing 1 to a PCICO_PLBBESRO field clears the field.

Preliminary

PCI Interface

17-45

Loading...

Loading...