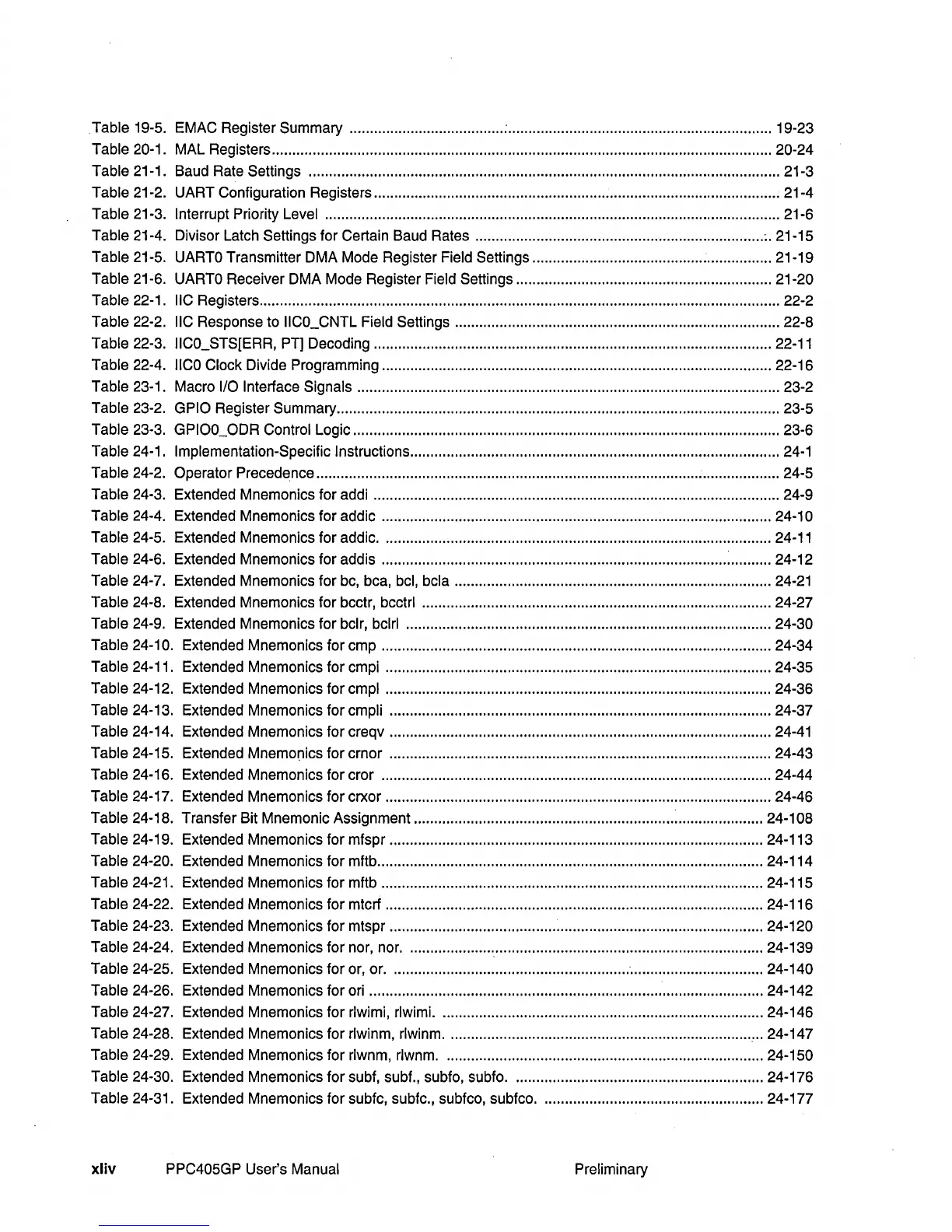

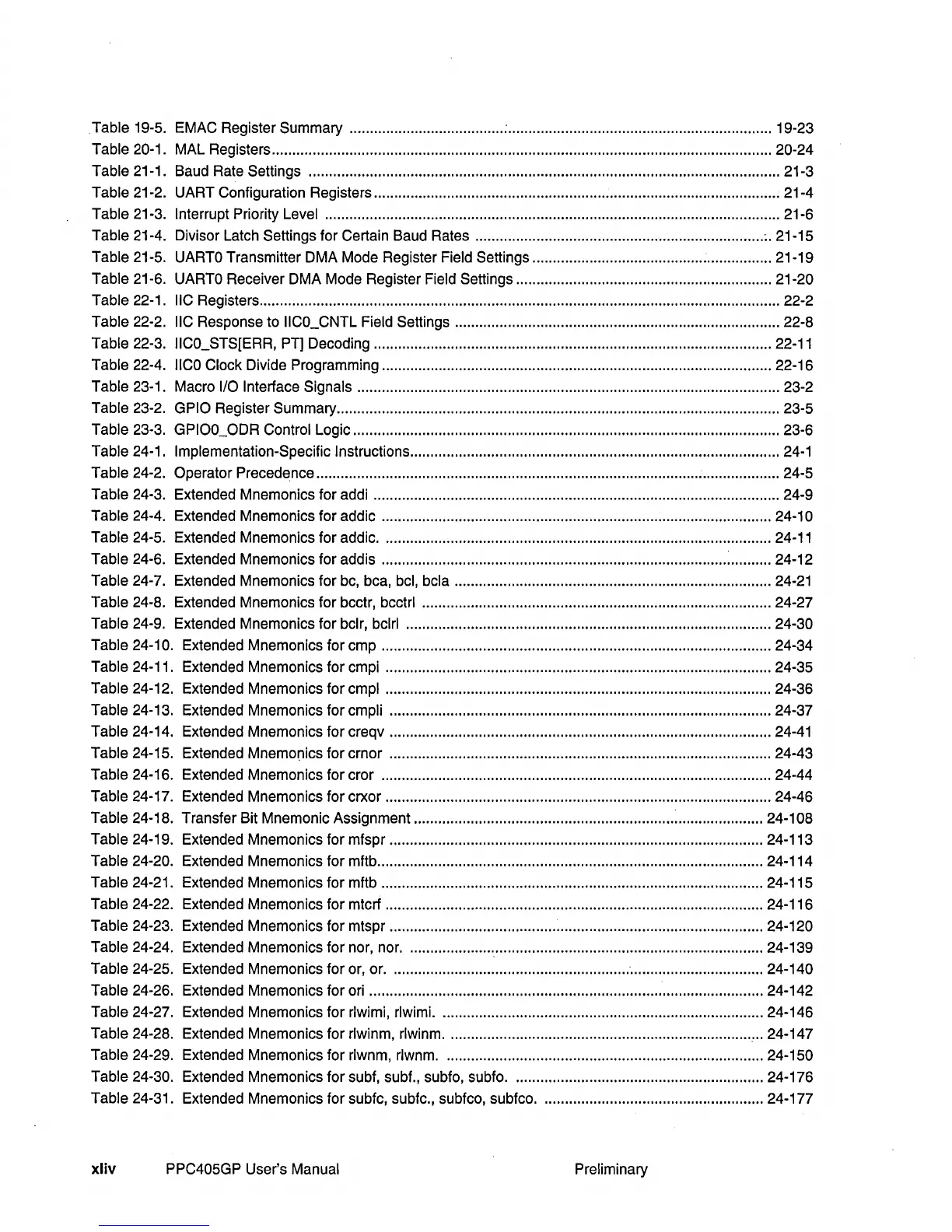

Table 19-5. EMAC Register Summary ...................................... : ................................................................. 19-23

Table 20-1. MAL Registers ........................................................................................................................... 20-24

Table 21-1. Baud Rate Settings .................................................................................................................... 21-3

Table 21-2. UART Configuration Registers .................................................................................................... 21-4

Table 21-3.

Interrupt Priority Level ................................................................................................................ 21-6

Table 21-4. Divisor Latch Settings for Certain Baud Rates .......................................................................

:.

21-15

Table 21-5.

UARTO

Transmitter DMA Mode Register Field Settings ........................................................... 21-19

Table 21-6.

UARTO

Receiver DMA Mode Register Field Settings ............................................................... 21-20

Table 22-1.

IIC Registers ................................................................................................................................ 22-2

Table 22-2.

IIC Response to IICO_CNTL Field Settings ................................................................................ 22-8

Table 22-3.

IICO_STS[ERR, PT] Decoding .................................................................................................. 22-11

Table 22-4.

IICO

Clock Divide Programming ................................................................................................ 22-16

Table 23-1. Macro

liD Interface Signals ........................................................................................................ 23-2

Table 23-2.

GPIO Register Summary ............................................................................................................. 23-5

Table 23-3.

GPIOO_ODR Control Logic ......................................................................................................... 23-6

Table 24-1. Implementation-Specific

Instructions ...........................................................................................

24-1

Table 24-2. Operator Precedence .................................................................................................................. 24-5

Table 24-3. Extended Mnemonics for addi .................................................................................................... 24-9

Table 24-4. Extended Mnemonics for addic ................................................................................................ 24-10

Table 24-5. Extended Mnemonics for addic ................................................................................................ 24-11

Table 24-6. Extended Mnemonics for addis ................................................................................................ 24-12

Table 24-7. Extended Mnemonics for bc, bca, bcl, bcla ..............................................................................

24-21

Table 24-8. Extended Mnemonics for bcctr, bcctrl ...................................................................................... 24-27

Table 24-9. Extended Mnemonics for bclr, bclrl .......................................................................................... 24-30

Table 24-10. Extended Mnemonics for cmp ................................................................................................ 24-34

Table 24-11. Extended Mnemonics for cmpi ............................................................................................... 24-35

Table 24-12. Extended Mnemonics for cmpl ............................................................................................... 24-36

Table 24-13. Extended Mnemonics for cmpli .............................................................................................. 24-37

Table 24-14. Extended Mnemonics for creqv .............................................................................................. 24-41

Table 24-15. Extended

Mnemonics for crnor .............................................................................................. 24-43

Table 24-16. Extended Mnemonics for cror ................................................................................................ 24-44

Table 24-17. Extended Mnemonics for crxor ............................................................................................... 24-46

Table 24-18. Transfer Bit Mnemonic Assignment ...................................................................................... 24-108

Table 24-19. Extended Mnemonics for mfspr ............................................................................................ 24-113

Table 24-20. Extended Mnemonics for mftb ............................................................................................... 24-114

Table 24-21. Extended Mnemonics for mftb .............................................................................................. 24-115

Table 24-22. Extended Mnemonics for mtcrf ............................................................................................. 24-116

Table 24-23. Extended Mnemonics for mtspr ............................................................................................ 24-120

Table 24-24. Extended Mnemonics for nor, nor ........................................................................................ 24-139

Table 24-25. Extended Mnemonics for or,

or

............................................................................................ 24-140

Table 24-26. Extended Mnemonics for ori ................................................................................................. 24-142

Table 24-27. Extended Mnemonics for rlwimi, rlwimi. ............................................................................... 24-146

Table 24-28. Extended Mnemonics for rlwinm, rlwinm .............................................................................. 24-147

Table 24-29. Extended Mnemonics for rlwnm, rlwnm ............................................................................... 24-150

Table 24-30. Extended Mnemonics for subf, subf., subfo, subfo .............................................................. 24-176

Table 24-31. Extended Mnemonics for subfc, subfc., subfco, subfco ....................................................... 24-177

xliv

PPC405GP User's Manual

Preliminary

Loading...

Loading...