19.7.1 Mode Register 0 (EMACO_MRO)

EMACO_MRO

defines

the

operating

modes

of

the

EMAC

that

can

be

changed

at

any

time

during

EMAC

operation.

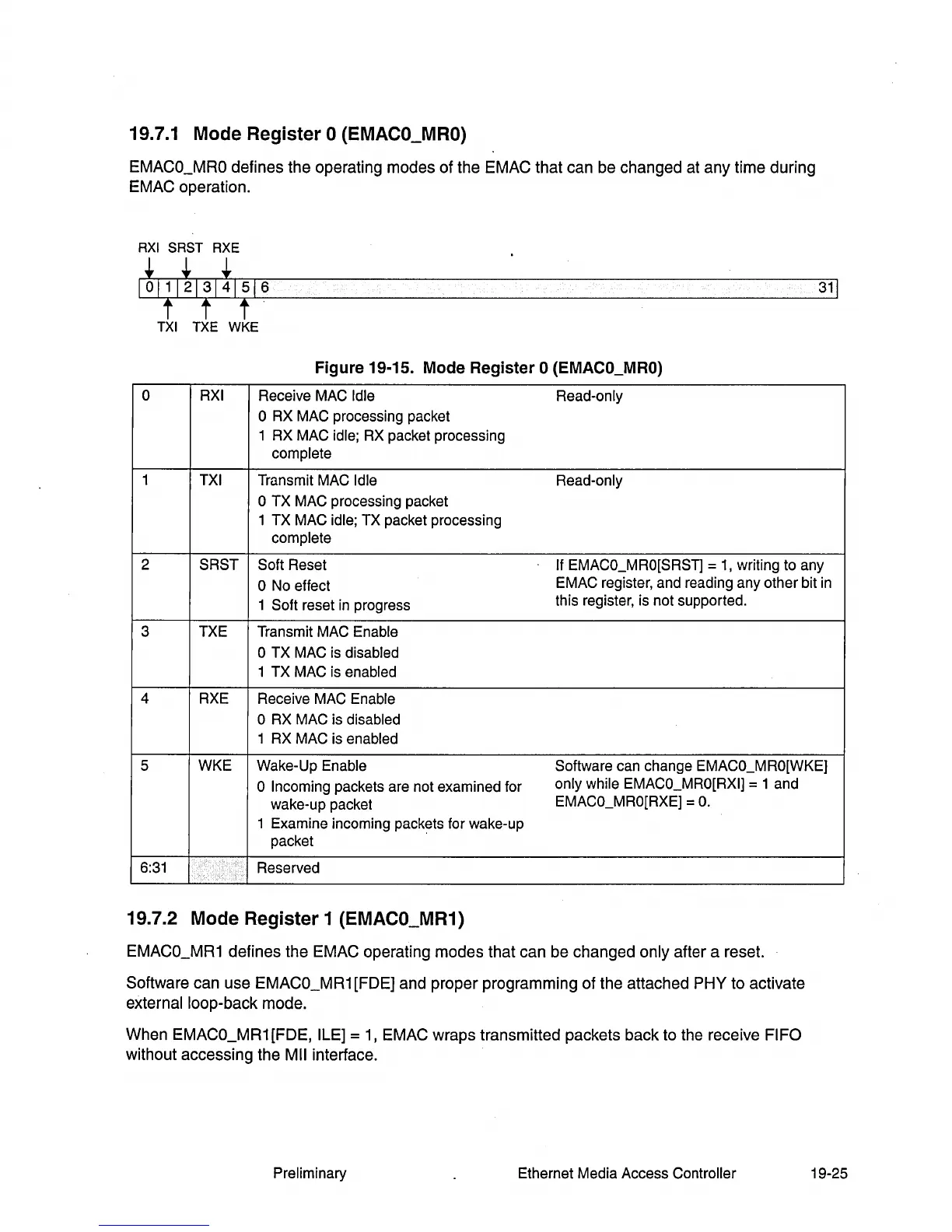

RXI

SRST

RXE

+ + +

t t t

TXI

TXE WKE

Figure 19·15. Mode Register 0 (EMACO_MRO)

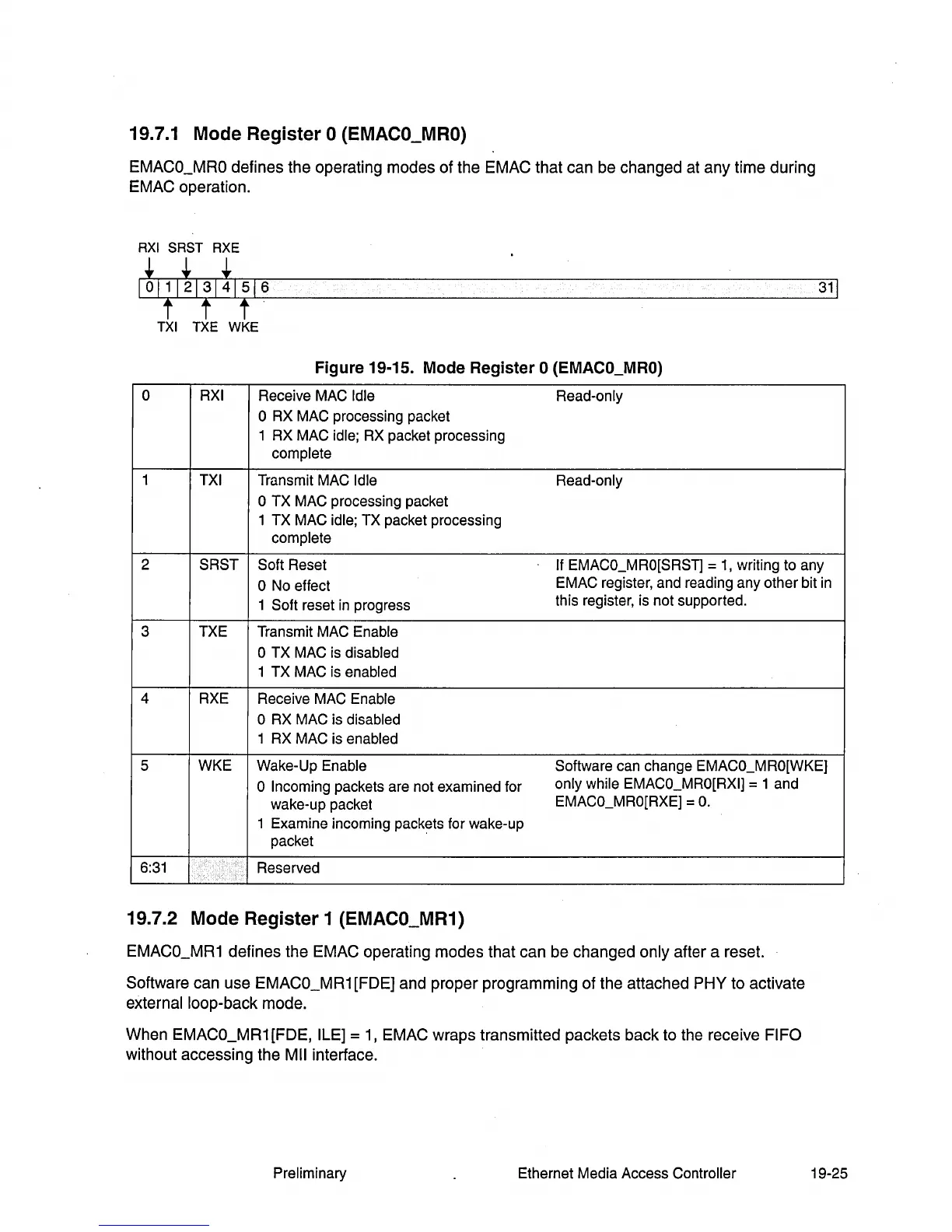

0

RXI

Receive MAC Idle Read-only

o RX MAC processing packet

1 RX MAC idle;

RX

packet processing

complete

1

TXI Transmit MAC Idle

Read-only

o TX MAC processing packet

1 TX MAC

idle; TX packet processing

complete

311

2 SRST

Soft

Reset

If

EMACO_MRO[SRST] =

1,

writing to any

o No effect

EMAC register, and reading any other bit

in

1 Soft reset

in

progress

this register, is not supported.

3 TXE Transmit MAC

Enable

o TX MAC

is

disabled

1 TX MAC

is

enabled

4 RXE

Receive MAC

Enable

o RX MAC is disabled

1 RX MAC is enabled

5 WKE Wake-Up Enable Software can change EMACO_MRO[WKE]

o Incoming packets are not examined for

only while EMACO_MRO[RXI] = 1 and

wake-up packet

EMACO_MRO[RXE]

=

O.

1 Examine incoming packets for wake-up

packet

6:31

Reserved

19.7.2 Mode Register 1 (EMACO_MR1)

EMACO_MR1

defines

the

EMAC

operating

modes

that

can

be

changed

only

after

a reset.

Software

can

use

EMACO_MR1 [FOE]

and

proper

programming

of

the

attached

PHY

to

activate

external

loop-back

mode.

When

EMACO_MR1 [FOE, ILE] =

1,

EMAC

wraps

transmitted

packets

back

to

the

receive

FIFO

without

accessing

the

Mil

interface.

Preliminary Ethernet Media Access Controller 19-25

Loading...

Loading...