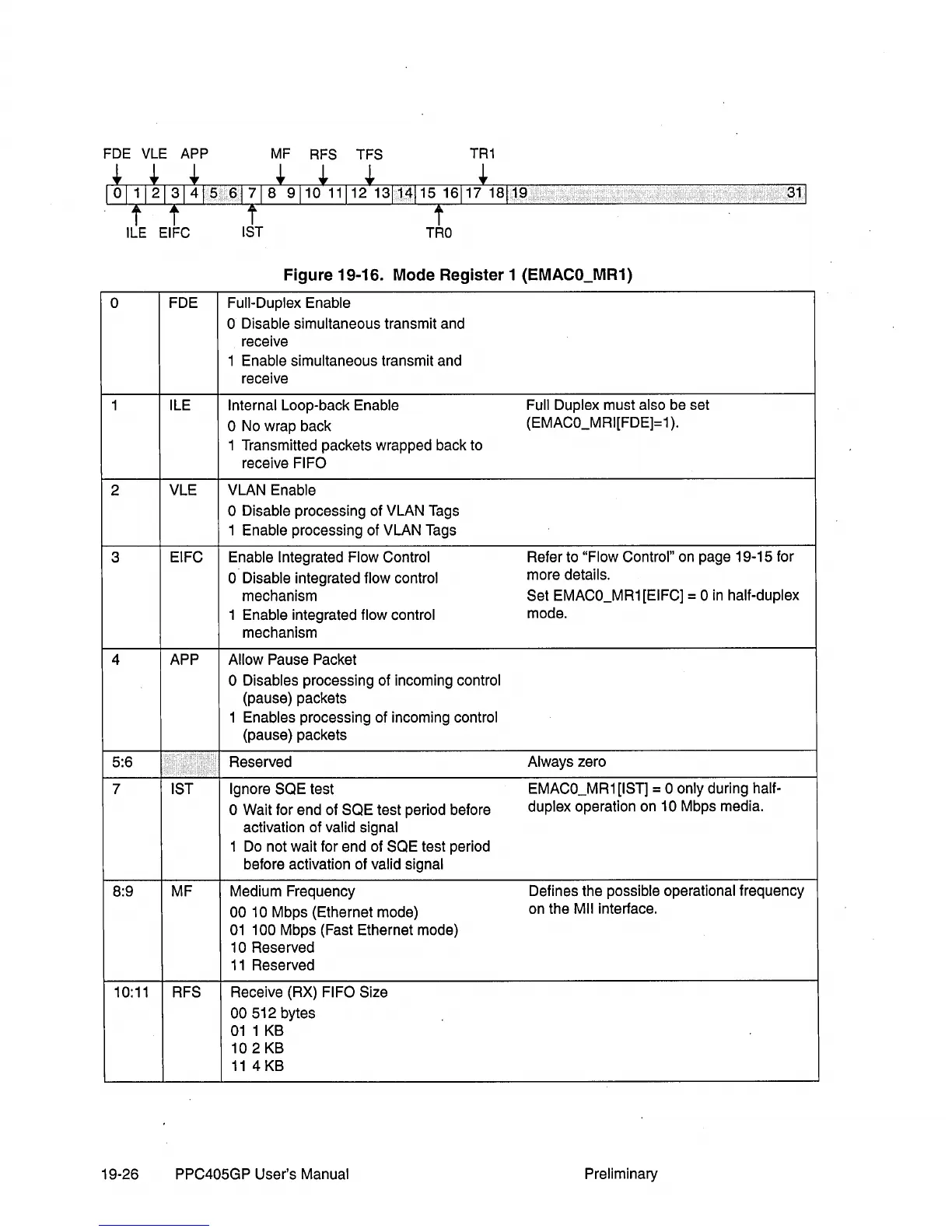

FDE

VLE

APP

..

.. ..

61718

9110 11112 1311411516117 18119

t t

31

1

t t

ILE

EIFC

1ST

TRO

Figure 19-16. Mode Register 1 (EMACO_MR1)

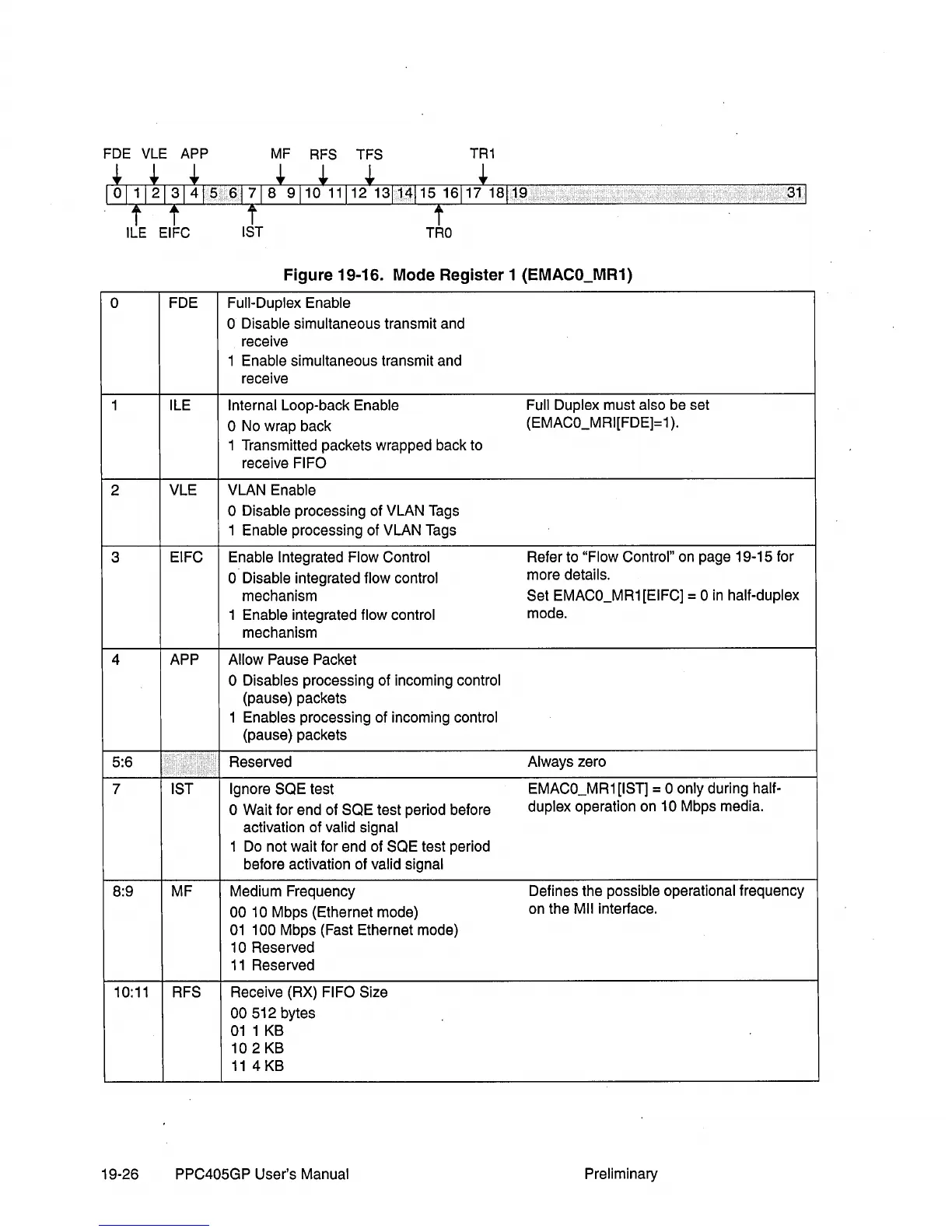

0 FDE

Full-Duplex Enable

o Disable simultaneous transmit and

receive

1

Enable simultaneous transmit and

receive

1

ILE Internal Loop-back Enable

Full Duplex

must also

be

set

o No wrap back

(EMACO_MRI[FDE]=1

).

1 Transmitted packets wrapped back to

receive

FIFO

2 VLE

VLAN Enable

o Disable processing of VLAN Tags

1

Enable processing of VLAN Tags

3

EIFC Enable Integrated Flow Control

Refer to "Flow Control"

on

page 19-15 for

o Disable integrated flow control

more details.

mechanism

Set

EMACO_MR1

[EIFC] = 0

in

half-duplex

1 Enable integrated flow control

mode.

mechanism

4

APP Allow Pause Packet

o Disables processing of incoming control

(pause) packets

1 Enables processing of incoming control

(pause) packets

5:6

...

Reserved Always zero

7

1ST

Ignore SOE test

EMACO_MR1

[1ST]

= 0 only during half-

o Wait for end of SOE test period before

duplex operation

on

10 Mbps media.

activation of

valid signal

1

Do

not wait for end of SOE test period

before activation of

valid signal

8:9 MF Medium Frequency

Defines the

possible operational frequency

00 10 Mbps (Ethernet mode)

on

the Mil interface.

01

100 Mbps (Fast Ethernet mode)

10 Reserved

11

Reserved

10:11 RFS

Receive (RX)

FIFO Size

00512

bytes

01

1 KB

102

KB

11

4 KB

19-26

PPC405GP User's Manual

Preliminary

Loading...

Loading...