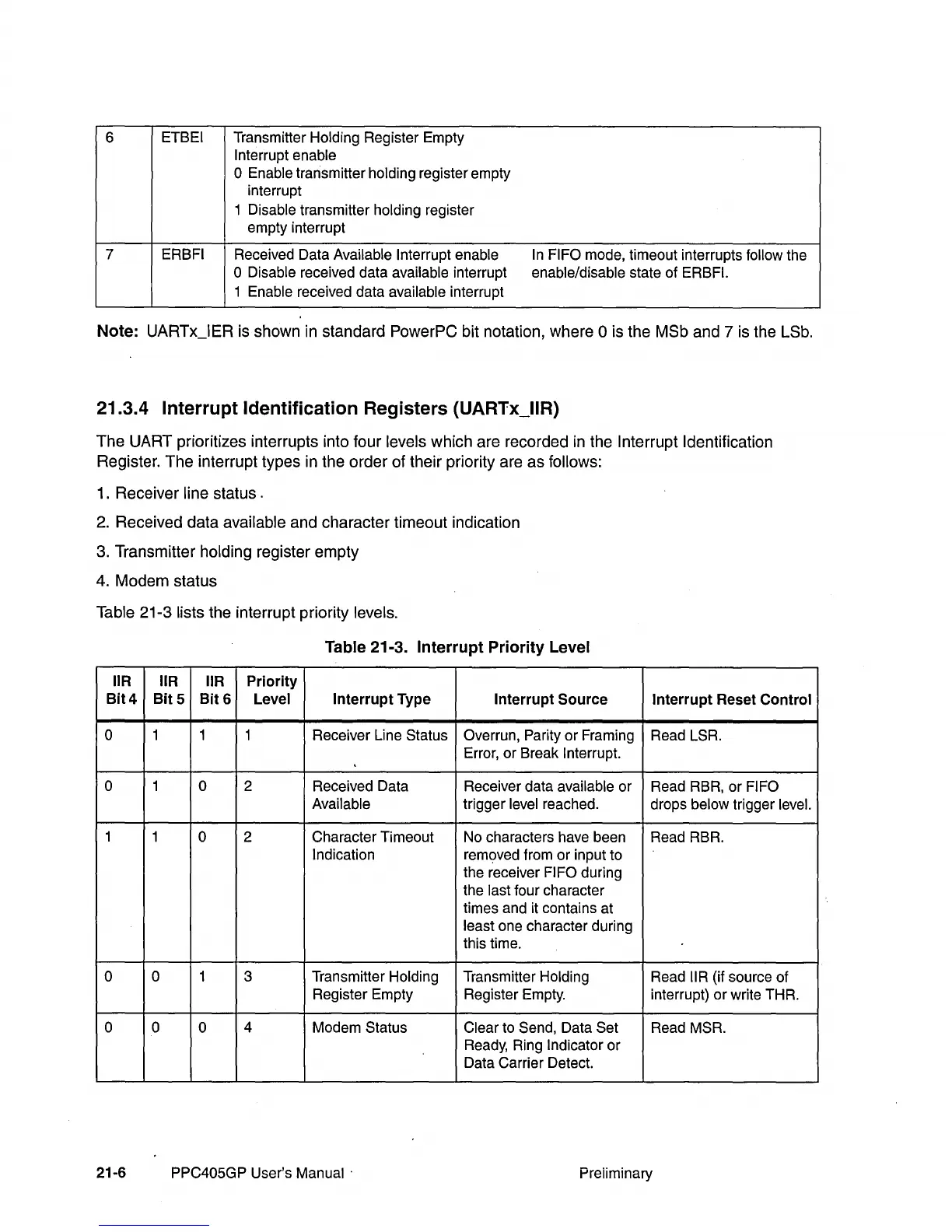

6

ETBEI Transmitter Holding Register Empty

Interrupt enable

o Enable transmitter holding register empty

interrupt

1 Disable transmitter holding register

empty interrupt

7 ERBFI

Received Data Available Interrupt enable

In

FIFO mode, timeout interrupts follow the

o Disable received data available interrupt

enable/disable state of ERBFI.

1 Enable received data available interrupt

Note: UARTx_IER is shown

in

standard PowerPC bit notation, where 0 is the MSb and 7 is the LSb.

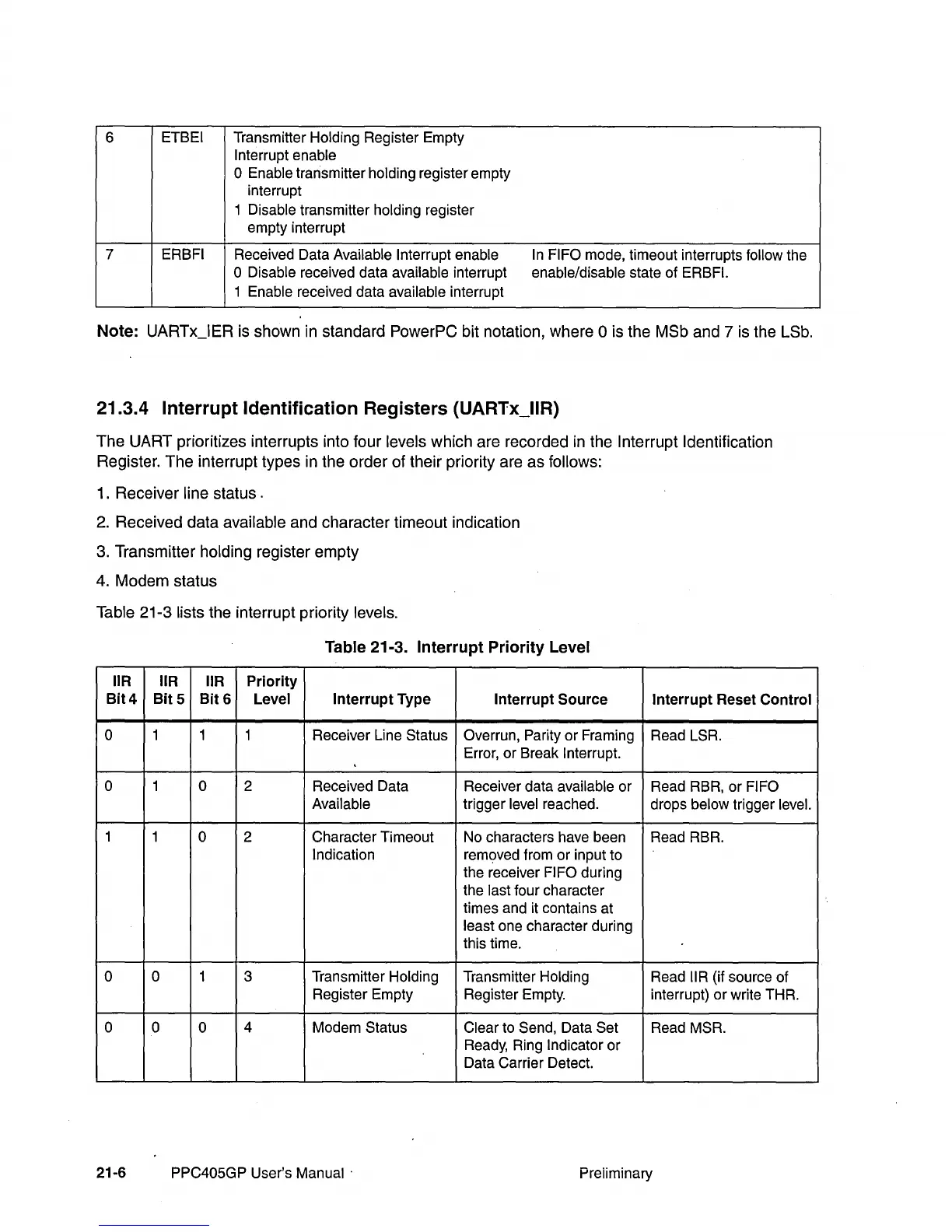

21.3.4

Interrupt

Identification

Registers (UARTx_IIR)

The UART prioritizes interrupts into four levels which are recorded

in

the Interrupt Identification

Register. The interrupt types

in

the order of their priority are as follows:

1. Receiver line status.

2.

Received data available and character timeout indication

3. Transmitter holding register empty

4. Modem status

Table 21-3

lists the interrupt priority levels.

Table 21-3.

Interrupt

Priority

Level

IIR IIR

IIR

Priority

Bit4

BitS

Bit

6

Level

Interrupt

Type

Interrupt

Source

Interrupt

Reset

Control

0 1 1 1 Receiver Line Status Overrun, Parity or Framing

Read

LSR.

Error, or Break Interrupt.

0 1 0 2

Received Data Receiver data available or Read RBR, or FIFO

Available trigger level reached.

drops below trigger level.

1

1

0 2 Character Timeout

No characters have been Read RBA.

Indication

removed from or input to

the receiver

FIFO during

the last four character

times and it contains at

least one character during

this time.

0 0 1 3 Transmitter Holding Transmitter Holding

Read IIR (if source of

Register Empty

Register Empty. interrupt) or write THR.

0 0

0

4 Modem Status

Clear to Send, Data Set Read MSR.

Ready, Ring Indicator or

Data Carrier Detect.

21-6 PPC405GP User's Manual .

Preliminary

Loading...

Loading...