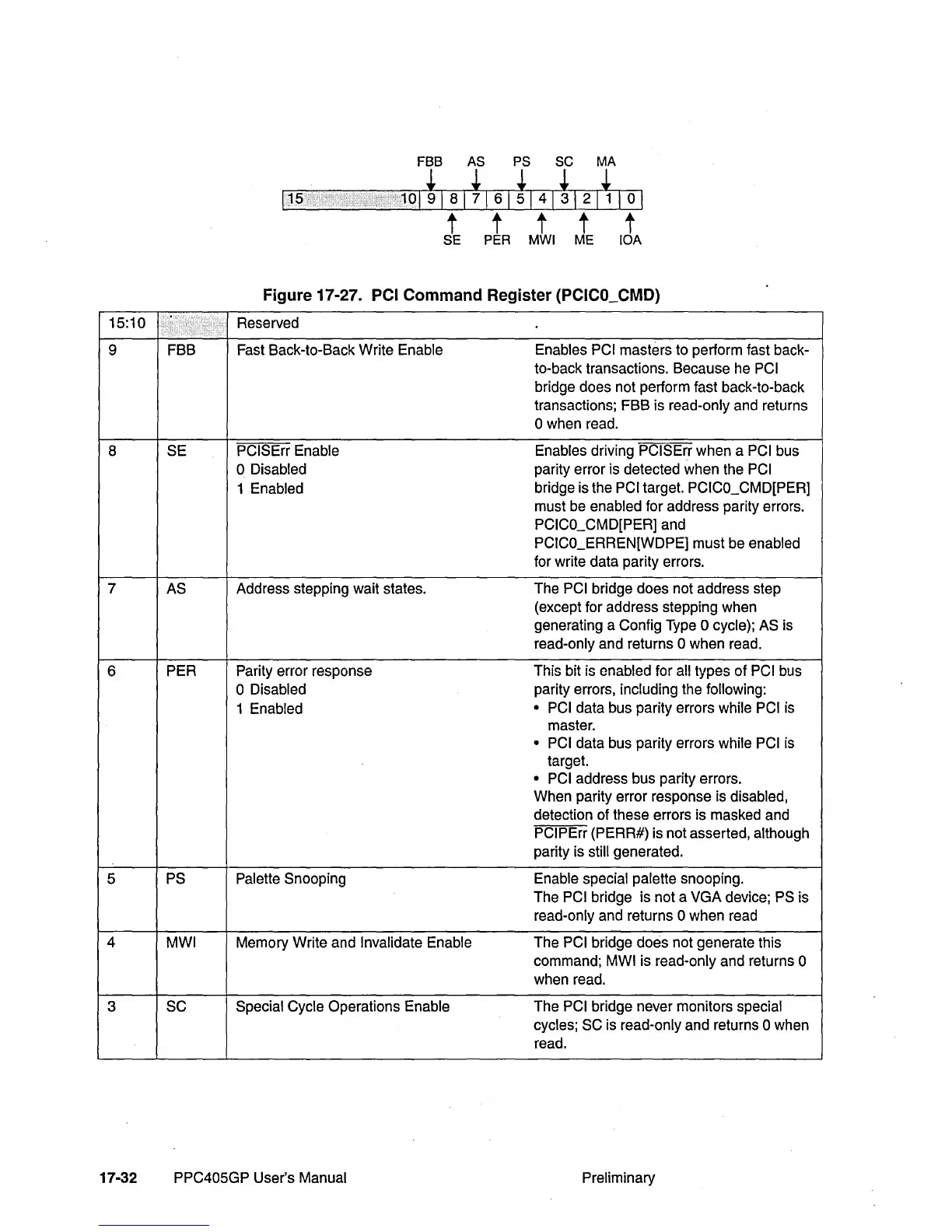

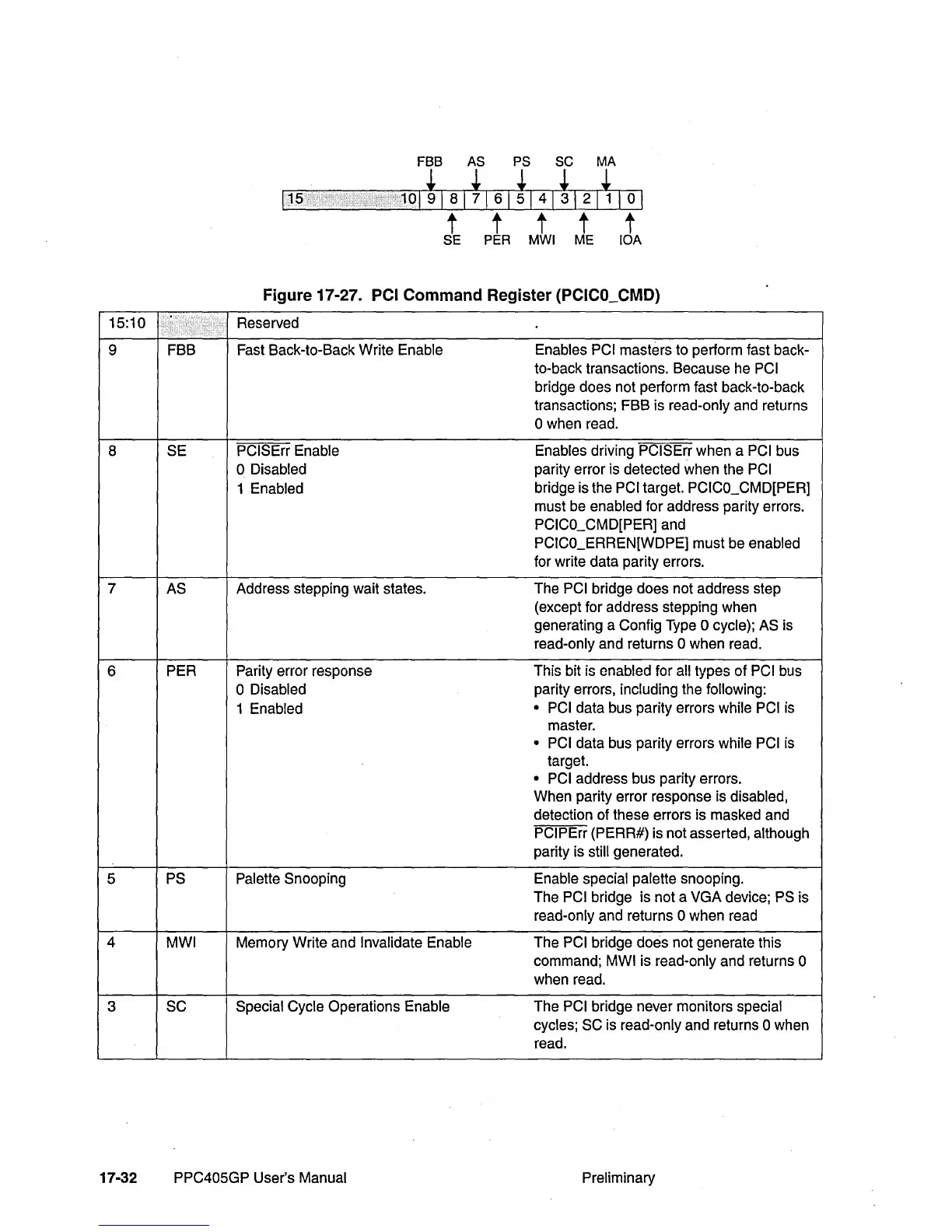

FBB

AS

PS

SC

MA

1

15

* * * * *

101

91

Sl

71

61

51

41

31

211

I 0 I

t t t t t

SE

PER

MWI

ME

IDA

Figure 17-27. PCI Command Register (PCICO_CMD)

15:10 Reserved

9

FBB Fast Back-to-Back Write Enable Enables PCI masters to perform fast back-

to-back transactions. Because he

PCI

bridge does not perform fast back-to-back

transactions; FBB is read-only and returns

o when read.

S SE

PCISErr Enable Enables driving PCISErr when a PCI bus

o Disabled parity error is detected when the PCI

1 Enabled

bridge is the PCI target. PCICO_CMD[PER]

must be enabled for address parity errors.

PCICO_CMD[PER] and

PCICO_ERREN[WDPE] must be enabled

for write data parity errors.

7

AS

Address stepping wait states. The PCI bridge does not address step

(except for address stepping when

generating a Config Type

0 cycle); AS is

read-only and returns

0 when read.

6

PER Parity error response This bit is enabled for all types of PCI bus

o Disabled

parity errors, including the following:

1 Enabled

• PCI data bus parity errors while PCI is

master.

• PCI data bus parity errors while PCI is

target.

• PCI address bus parity errors.

When parity error response is disabled,

detection of these errors is masked and

PCIPErr (PERR#) is not asserted, although

parity is still generated.

5

PS

Palette Snooping Enable special palette snooping.

The

PCI bridge is not a VGA device; PS is

read-only and returns

0 when read

4

MWI

Memory Write and Invalidate Enable

The PCI bridge does not generate this

command;

MWI is read-only and returns 0

when read.

3 SC

Special Cycle Operations Enable The PCI bridge never monitors special

cycles;

SC is read-only and returns 0 when

read.

17-32 PPC405GP User's Manual Preliminary

Loading...

Loading...