2 ME Master Enable Enables PCI bridge-to-master cycles on

o Disabled the PCI bus. When

ME

is 0, the PCI bridge

1 Enabled

only

responds as a PLB slave to

PCICO_CFGADDR, PCICO_CFGDATA,

and PCI bridge local configuration register

access. Except for configuration cycles, the

P.CI

bridge cannot master cycles to the PCI

bus.

If

the pin strapping setting reflected

in

CPCO_PSR[RL] =

1,

ME resets to 1.

1

MA

Memory Access Controls PCI bridge response as a PCI

o Disabled memory target. MA is disabled at reset.

1 Enabled

0

lOA

1/0

Access Controls the PCI bridge response as a PCI

I/O

target. The PCI bridge does not

respond to

1/0

space accesses; lOA is

read-only and returns 0 when read.

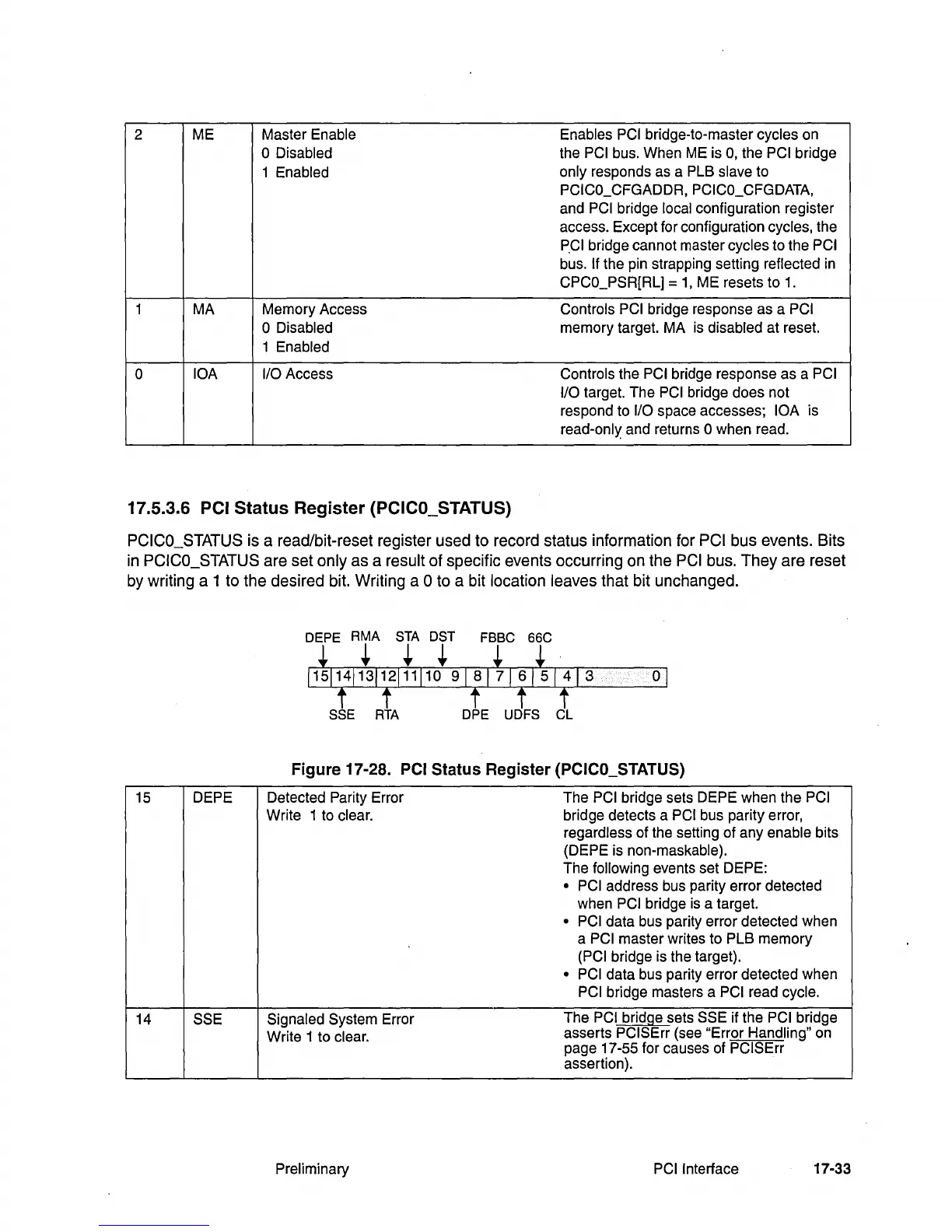

17.5.3.6 PCI Status Register (PCICO_STATUS)

PCICO_STATUS is a read/bit-reset register used to record status information for PCI bus events. Bits

in

PCICO_STATUS are set only as a result of specific events occurring on the

PCI

bus. They are reset

by writing a 1 to the desired bit. Writing a

° to a bit location leaves that bit unchanged.

OEPE RMA

STA

OST

FBBC 66C

i + + + i

i·

1151141131121111109181716151413

01

t t t t t

SSE

RTA

OPE

UOFS CL

Figure 17-28. PCI Status Register (PCICO_STATUS)

15 DEPE Detected Parity Error The PCI bridge sets DEPE when the PCI

Write 1 to clear. bridge detects a PCI bus parity error,

regardless of the setting of any enable bits

(DEPE is non-maskable).

The

following events set DEPE:

• PCI address bus parity error detected

when

PCI bridge

is

a target.

• PCI data bus parity error detected when

a

PCI master writes to PLB memory

(PC

I bridge is the target).

• PCI data bus parity error detected when

PCI bridge masters a PCI read cycle.

14

SSE

Signaled System Error

The

PCI bridge sets SSE if the PCI bridge

Write

1 to clear.

asserts PCISErr (see "Error Handling" on

page

17-55 for causes of PCISErr

assertion).

Preliminary PCI Interface

17-33

Loading...

Loading...