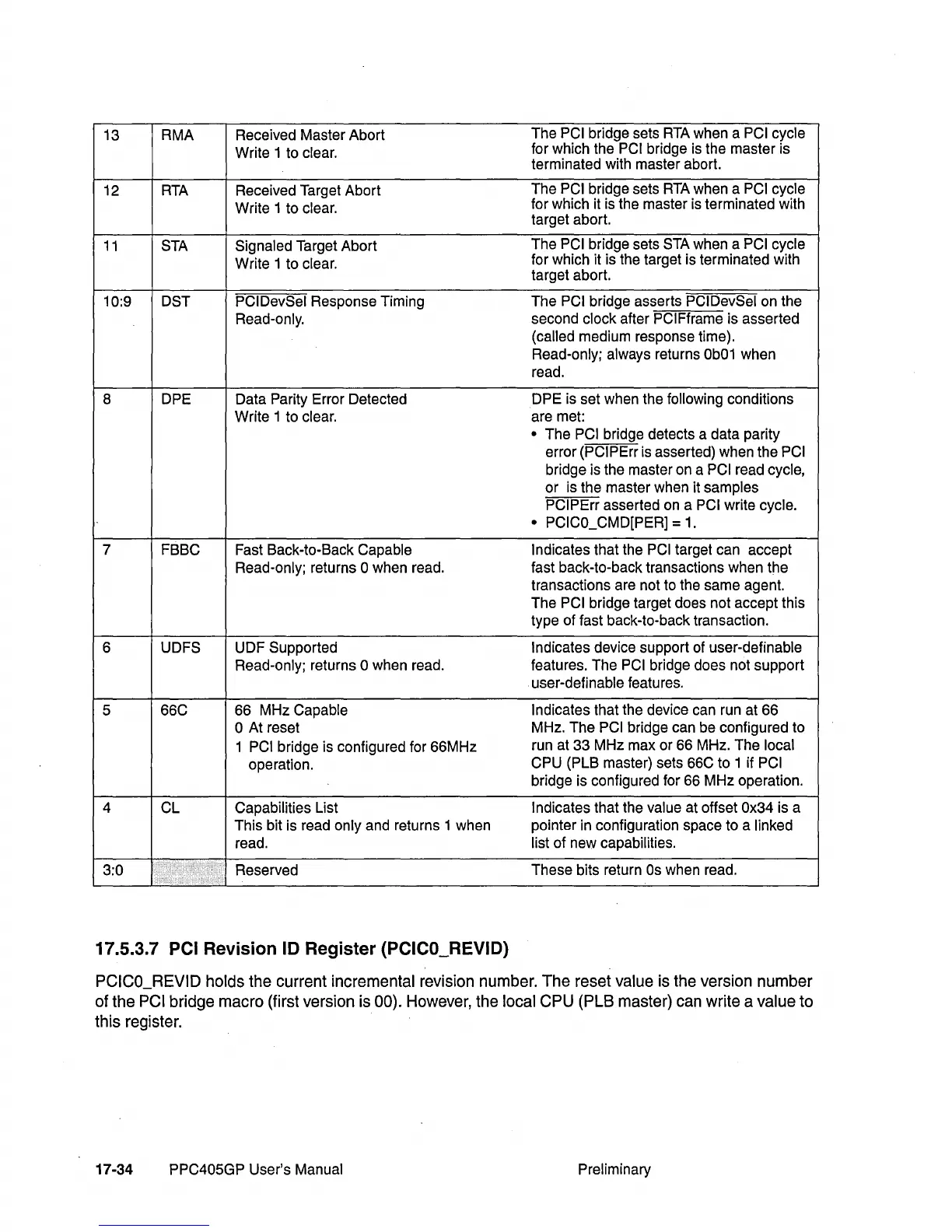

13 RMA

Received Master Abort

The

PCI bridge sets

RTA

when a PCI cycle

Write 1 to clear.

for which the PCI bridge is the master is

terminated with master abort.

12

RTA

Received Target Abort

The

PCI bridge sets

RTA

when a PCI cycle

Write 1 to clear.

for which it is the master is terminated with

target abort.

11

STA Signaled Target Abort

The

PCI bridge sets

STA

when a PCI cycle

Write 1 to clear.

for which it is the target is terminated with

target abort.

10:9 DST

PCIDevSel Response Timing

The PCI bridge asserts PCIDevSel on the

Read-only.

second clock after PCIFframe is asserted

(called medium response time).

Read-only; always returns

Ob01

when

read.

8 DPE Data Parity Error Detected

DPE is set when the following conditions

Write 1 to

clear. are met:

• The PCI bridge detects a data parity

error

(PCIPErr is asserted) when the PCI

bridge is the master on a PCI read cycle,

or is the master when it samples

PCIPErr

asserted

on

a PCI write cycle.

• PCICO_CMD[PER]

=

1.

7

FBBC

Fast Back-to-Back Capable Indicates that the PCI target can accept

Read-only; returns 0 when read.

fast back-to-back transactions when the

transactions are not to the same agent.

The

PCI bridge target does not accept this

type of fast back-to-back transaction.

6

UDFS UDF Supported

Indicates device support of user-definable

Read-only;

returns 0 when read.

features. The PCI bridge does not support

user-definable features.

5 66C

66 MHz

Capable

Indicates that the device can run at 66

o At reset

MHz. The PCI bridge can be configured to

1

PCI bridge is configured for 66MHz

run at 33 MHz max or 66 MHz. The

local

operation.

CPU (PLB master) sets 66C to 1 if PCI

bridge is configured for 66 MHz operation.

4

CL Capabilities List

Indicates that the value at offset

Ox34

is a

This bit is read

only and returns 1 when pointer in configuration space to a linked

read . list of new capabilities.

3:0

....•.•....

....

Reserved These bits return

Os

when read.

..

17.5.3.7 PCI Revision

10

Register (PCICO_REVIO)

PCICO_REVID holds the current incremental revision number. The reset value is the version number

of the

PCI bridge macro (first version is 00). However, the local CPU (PLB master) can write a value to

this register.

17-34 PPC405GP User's Manual Preliminary

Loading...

Loading...