D5.1 AArch64 PMU register summary

The PMU counters and their associated control registers are accessible in the AArch64 Execution state

with MRS and MSR instructions.

The following table gives a summary of the Cortex-A76 PMU registers in the AArch64 Execution state.

For those registers not described in this chapter, see the Arm

®

Architecture Reference Manual Armv8, for

Armv8-A architecture profile.

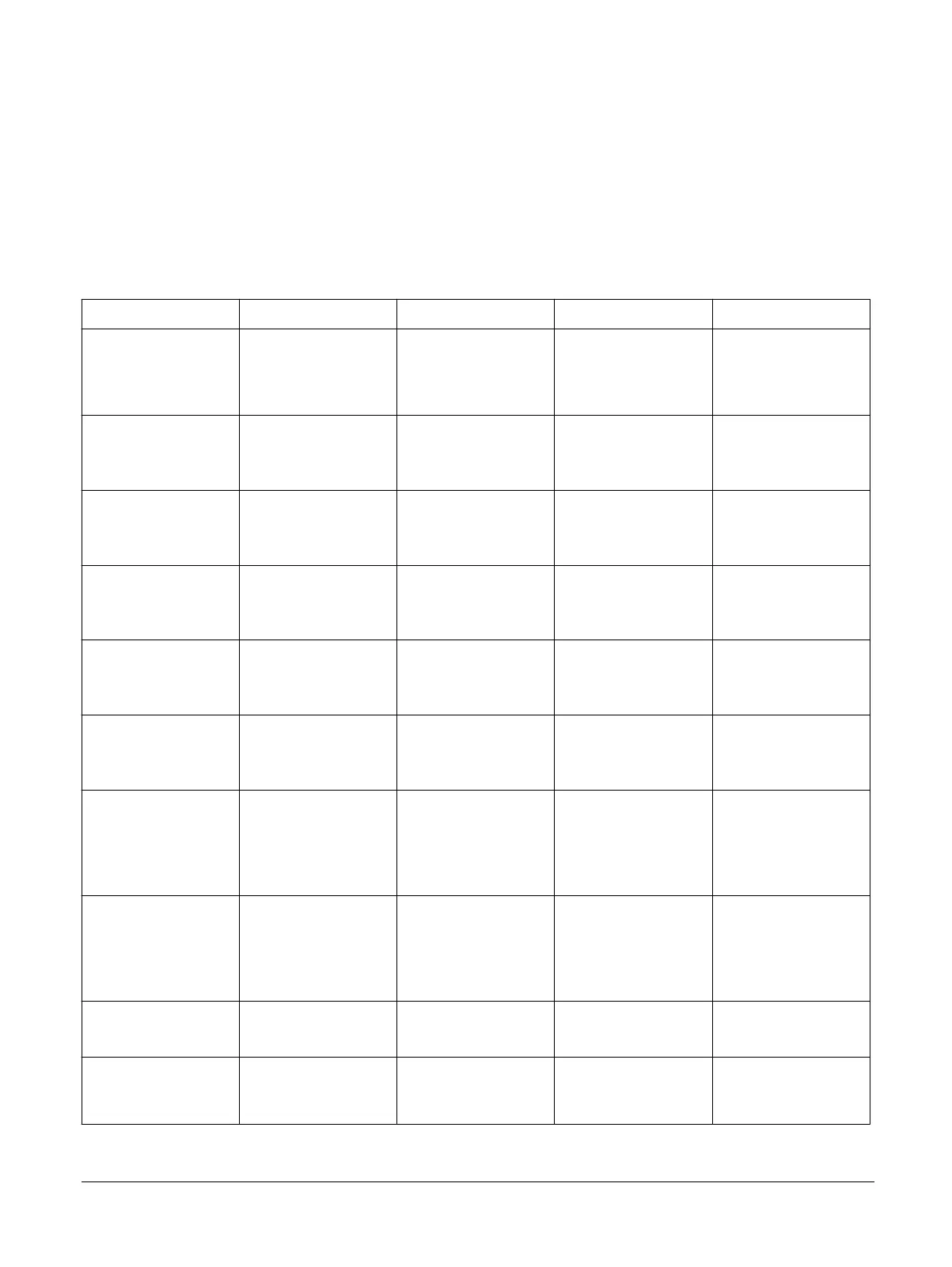

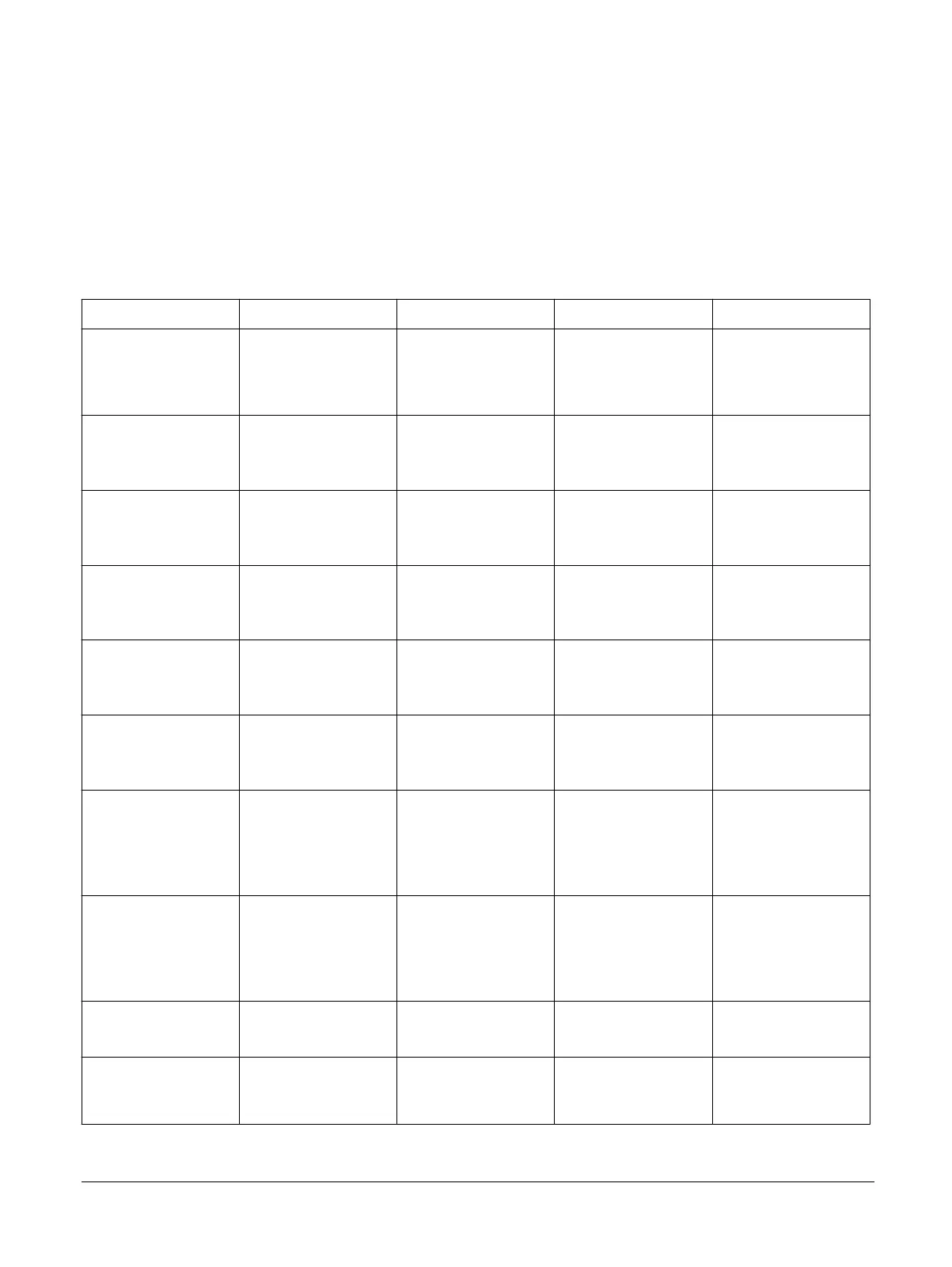

Table D5-1 PMU register summary in the AArch64 Execution state

Name Type Width Reset Description

PMCR_EL0 RW 32

0x410B30XX

D5.4 PMCR_EL0,

Performance Monitors

Control Register, EL0

on page D5-453

PMCNTENSET_EL0 RW 32 UNK

Performance Monitors

Count Enable Set

Register

PMCNTENCLR_EL0 RW 32 UNK

Performance Monitors

Count Enable Clear

Register

PMOVSCLR_EL0 RW 32 UNK

Performance Monitors

Overflow Flag Status

Register

PMSWINC_EL0 WO 32 UNK

Performance Monitors

Software Increment

Register

PMSELR_EL0 RW 32 UNK

Performance Monitors

Event Counter Selection

Register

PMCEID0_EL0 RO 64

0xF7FF0F3F

D5.2 PMCEID0_EL0,

Performance Monitors

Common Event

Identification Register 0,

EL0 on page D5-448

PMCEID1_EL0 RO 64

0x0000BE7F

D5.3 PMCEID1_EL0,

Performance Monitors

Common Event

Identification Register 1,

EL0 on page D5-451

PMCCNTR_EL0 RW 64 UNK

Performance Monitors

Cycle Count Register

PMXEVTYPER_EL0 RW 32 UNK Performance Monitors

Selected Event Type and

Filter Register

D5 AArch64 PMU registers

D5.1 AArch64 PMU register summary

100798_0300_00_en Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D5-446

Non-Confidential

Loading...

Loading...