P.3.47

Date Code 20151029 Protection Manual SEL-411L Relay

Protection Functions

87L Differential Elements

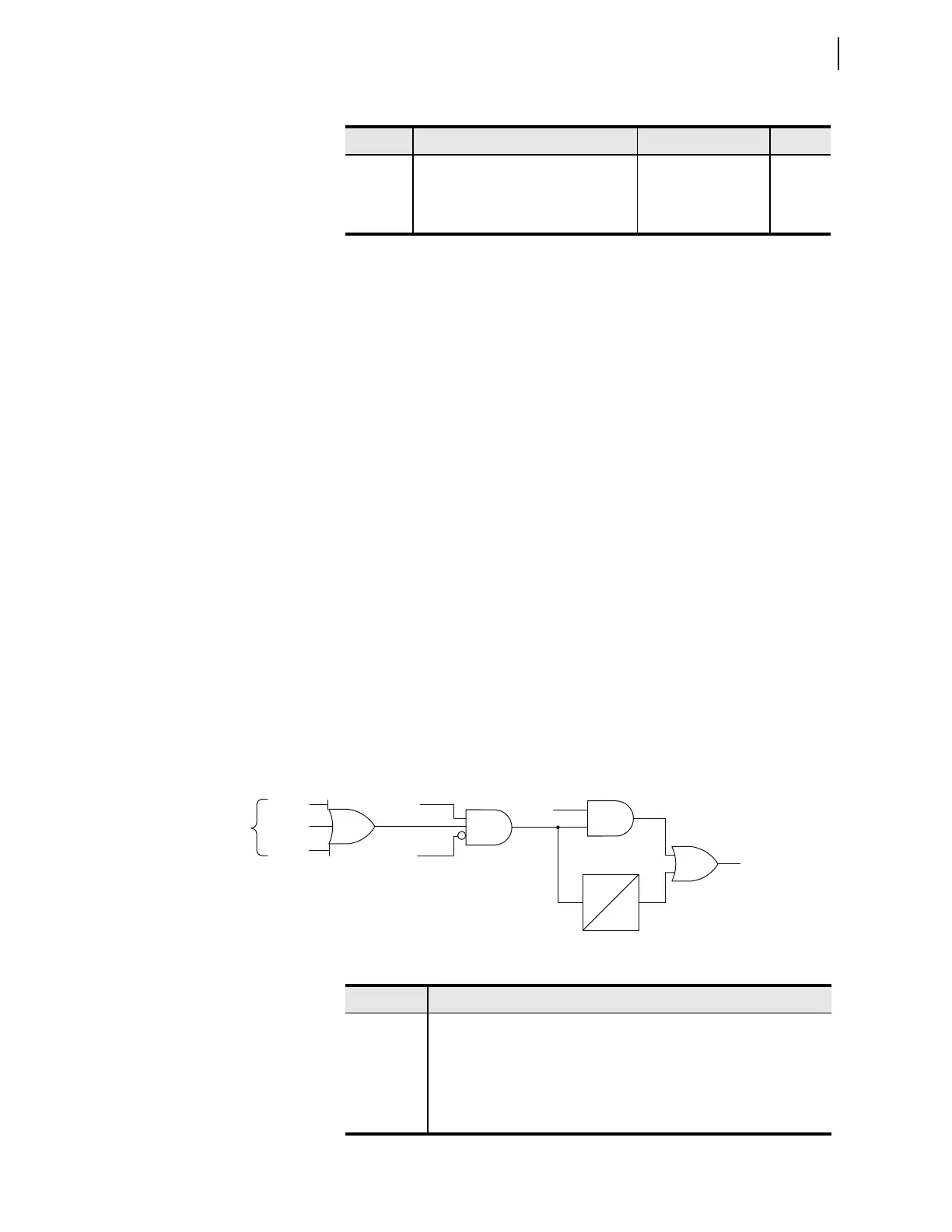

As Figure 3.26 shows, received 87DTT bits are available as Relay Word bits.

If any active channel receives the 87DTT bit, the direct transfer tripping is

enabled via the E87DTT SEL

OGIC control equation, and the relay is not in the

stub bus mode, the 87DTTRX Relay Word bit will assert to operate the trip

logic. The 87DTTRX bit asserts instantaneously if the disturbance detection

provides validation or after 0.75-cycle delay if the disturbance detector fails to

pick up.

The combination of disturbance detection supervision and time delay makes

the 87DTT application very secure against undetected bit errors in the

received 87L packets. Received 87DTT bits must be validated with the change

in local currents, or at least three consecutive packets must show the 87DTT

bit asserted. With the 32-bit BCH protecting the integrity of each packet (see

87L Theory of Operation for more details), it becomes unlikely beyond any

practical concern that three consecutive packets will spuriously assert the

87DTT bit and the BCH check will fail three times to detect such spurious

assertion.

Program E87DTT to 1 in three-terminal applications (E87CH = 3SS or 3SM).

3SM cases only apply in the event of a failed communications channel

between two of the relays.

You can dynamically inhibit 87DTT by programming the E87DTT SEL

OGIC

control equation if channel quality becomes problematic, such as might

happen if the lost packet count or other impairments are beyond expected

values.

You can also use one of the user-programmable 87L communications bits to

program custom 87DTT logic if necessary (see User-Programmable 87L

Communications Bits for more details).

Figure 3.26 87DTT Logic

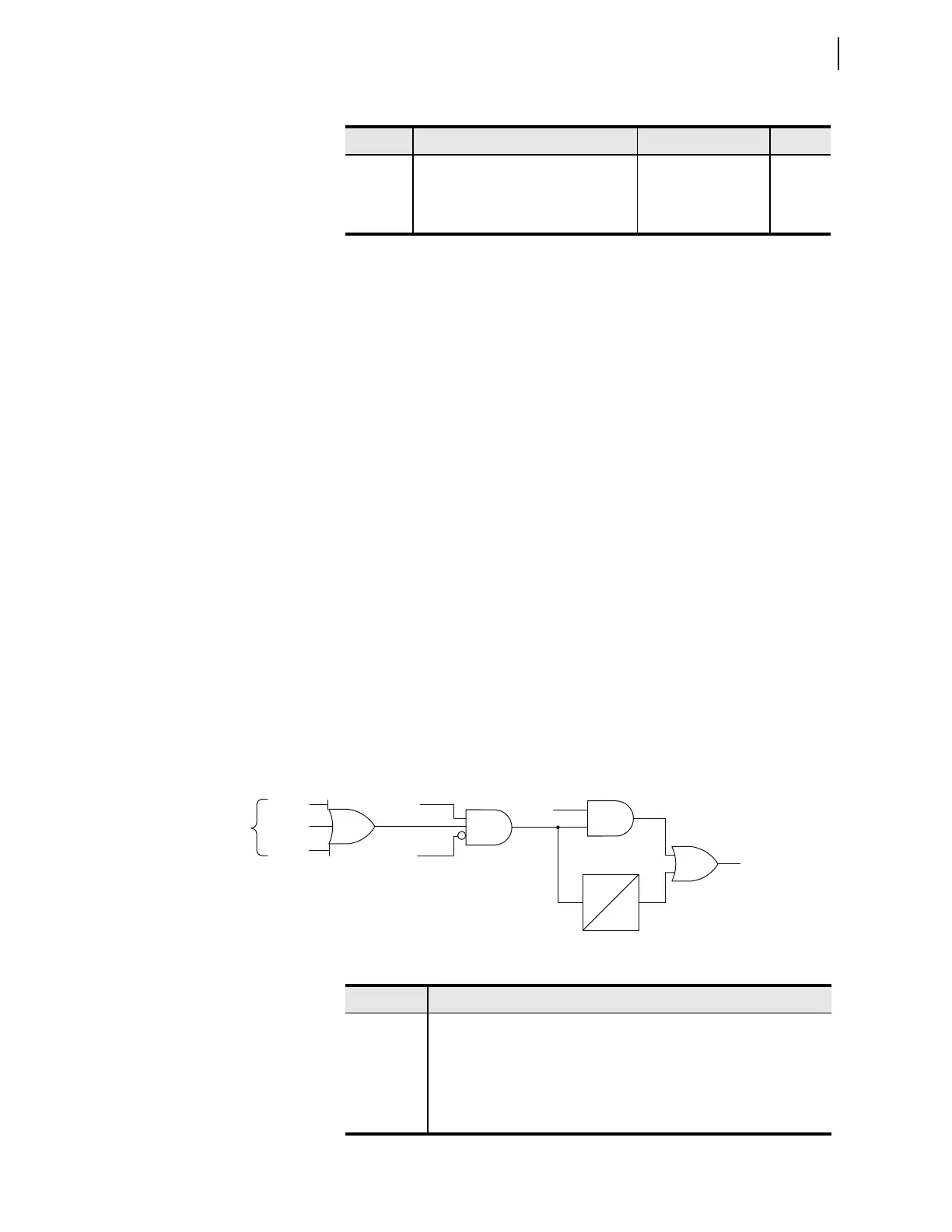

Table 3.15 87DTT Direct Transfer Tripping Settings

Setting Description Range Default

E87DTT Enable 87 direct transfer trip receive

logic

SELOGIC control

equation

1

E51DTT Enable transmitting 87DTT from differ-

ential time-overcurrent elements

Y, N N

87DTT received,

all active channels

Relay Word Bits

87DTT1

87DTT2

87DTT3

Relay Word Bits

E87DTT

ESTUB

Relay Word Bit

87DD

Relay Word Bit

87DTTRX

(to trip logic)

0.75

cyc

0

Table 3.16 87DTT Direct Transfer Tripping Relay Word Bits

Name Description

E87DTT 87 direct transfer trip receive enabled

87DTT1 87 direct transfer trip received on the 87L Channel 1

87DTT2 87 direct transfer trip received on the 87LChannel 2

87DTT3 87 direct transfer trip received on the 87L Channel 3 (Ethernet only)

87DTTRX 87 direct transfer trip received and validated

Loading...

Loading...