RM0367 Rev 7 153/1043

RM0367 Power control (PWR)

172

6.3 Low-power modes

By default, the microcontroller is in Run mode after a system or a power-on reset. In Run

mode the CPU is clocked by HCLK and the program code is executed. Several low-power

modes are available to save power when the CPU does not need to be kept running, for

example when waiting for an external event. It is up to the user to select the mode that gives

the best compromise between low-power consumption, performance, short startup time and

available wakeup sources.

The devices feature five low-power modes:

• Low-power run mode: regulator in low-power mode, limited clock frequency, limited

number of peripherals running (refer to Section 6.3.4)

• Sleep mode: Cortex

®

-M0+ core stopped, peripherals kept running (refer to

Section 6.3.7)

• Low-power sleep mode: Cortex

®

-M0+core stopped, limited clock frequency, limited

number of peripherals running, regulator in low-power mode, Flash stopped ((refer to

Section 6.3.8))

• Stop mode (all clocks are stopped, regulator running, regulator in low-power mode

(refer to Section 6.3.9)

• Standby mode: V

CORE

domain powered off ((refer to Section 6.3.10))

In addition, the power consumption in Run mode can be reduced by one of the following

means:

• Slowing down the system clocks

• Gating the clocks to the APBx and AHBx peripherals when they are unused.

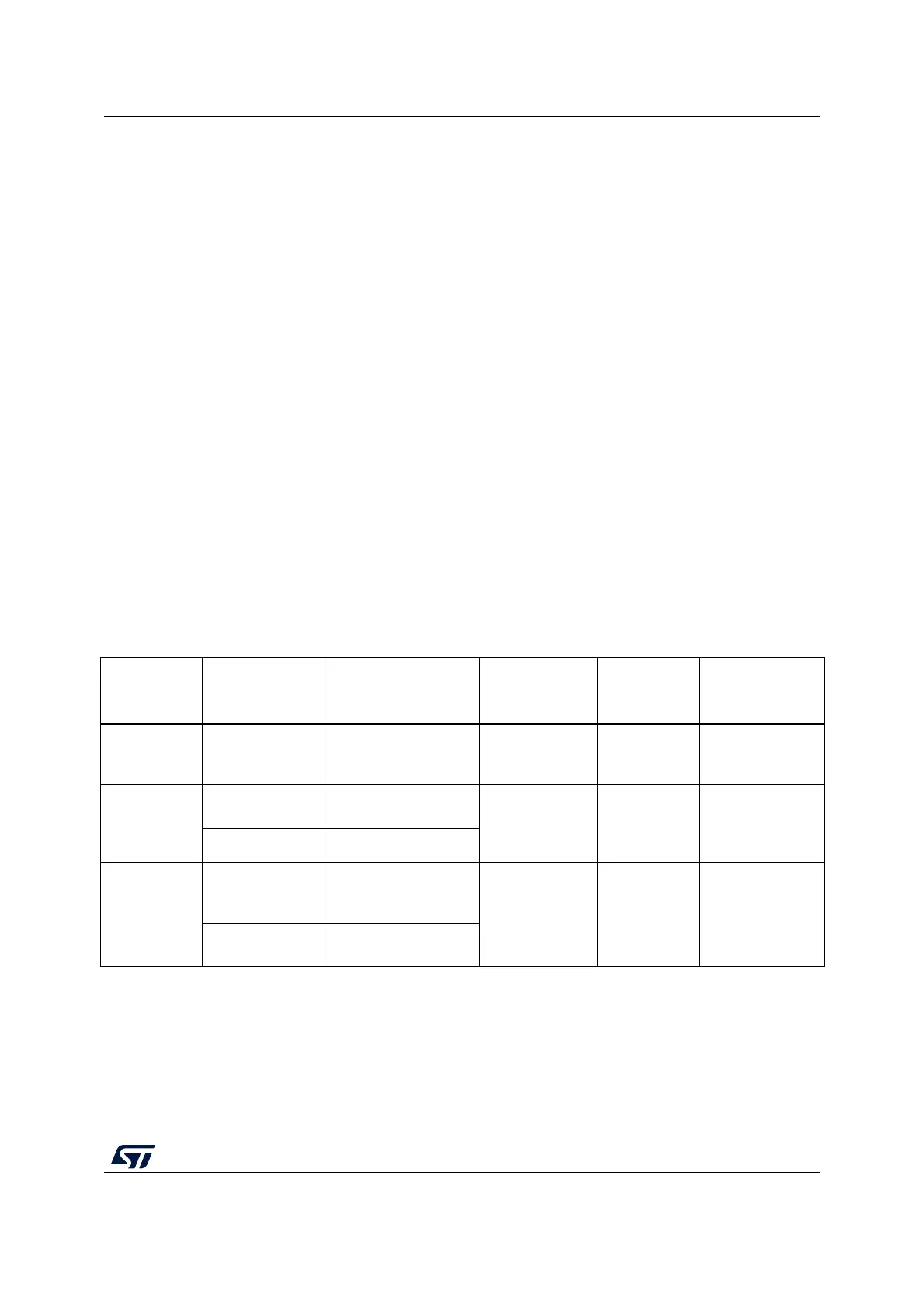

Table 32. Summary of low-power modes

Mode name Entry Wakeup

Effect on V

CORE

domain clocks

Effect on V

DD

domain

clocks

Voltage regulator

Low-power

run

LPSDSR and

LPRUN bits +

Clock setting

The regulator is forced

in Main regulator (1.8

V)

None None

In low-power

mode

Sleep

(Sleep now or

Sleep-on-exit)

WFI or Return

from ISR

Any interrupt

CPU CLK OFF

no effect on other

clocks or analog

clock sources

None ON

WFE Wakeup event

Low-power

sleep (Sleep

now or Sleep-

on-exit)

LPSDSR bits +

WFI or Return

from ISR

Any interrupt

CPU CLK OFF

no effect on other

clocks or analog

clock sources,

Flash CLK OFF

None

In low-power

mode

LPSDSR bits +

WFE

Wakeup event

Loading...

Loading...