RM0367 Rev 7 329/1043

RM0367 Analog-to-digital converter (ADC)

352

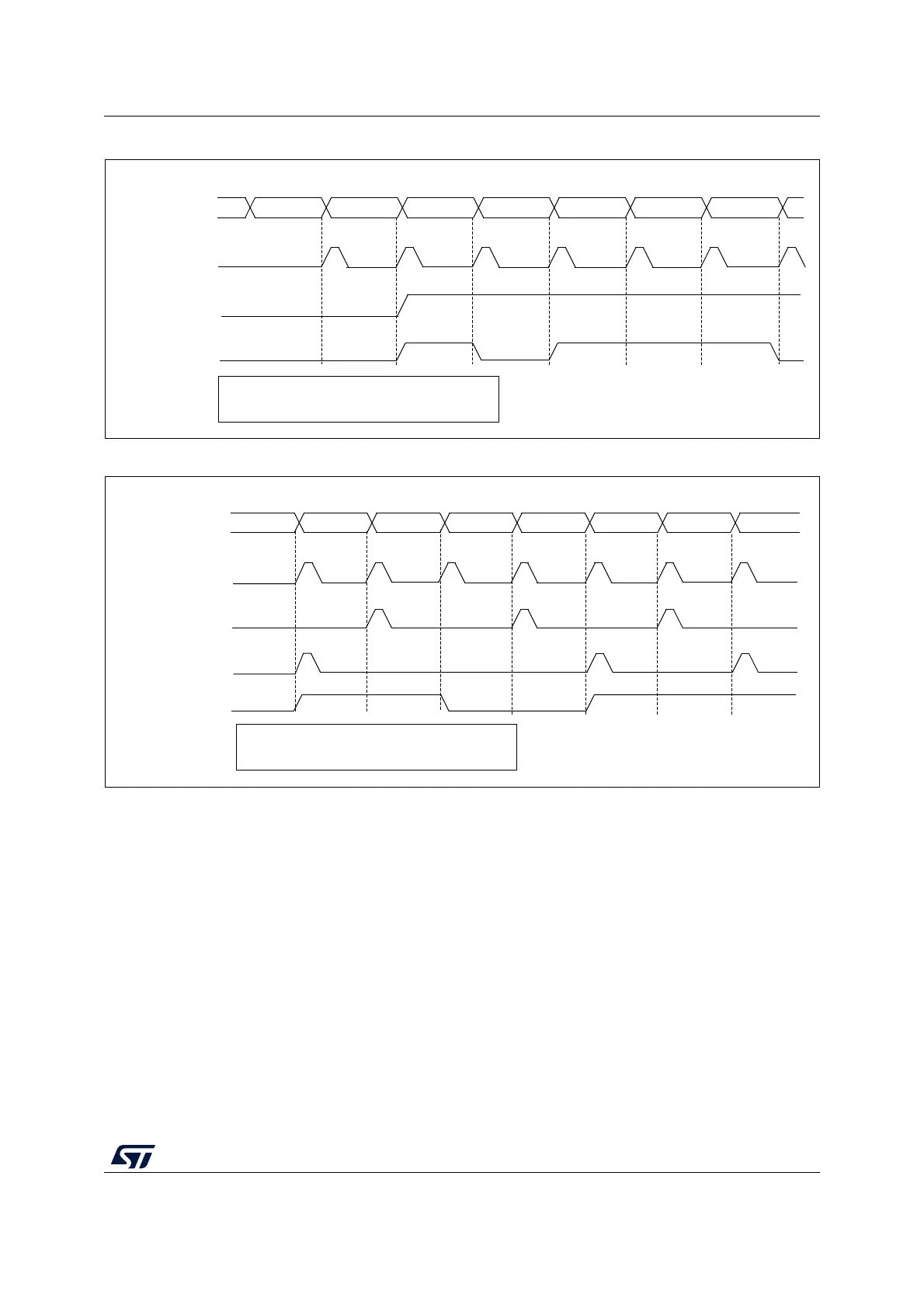

Figure 51. ADC_AWD1_OUT signal generation (AWD flag not cleared by software)

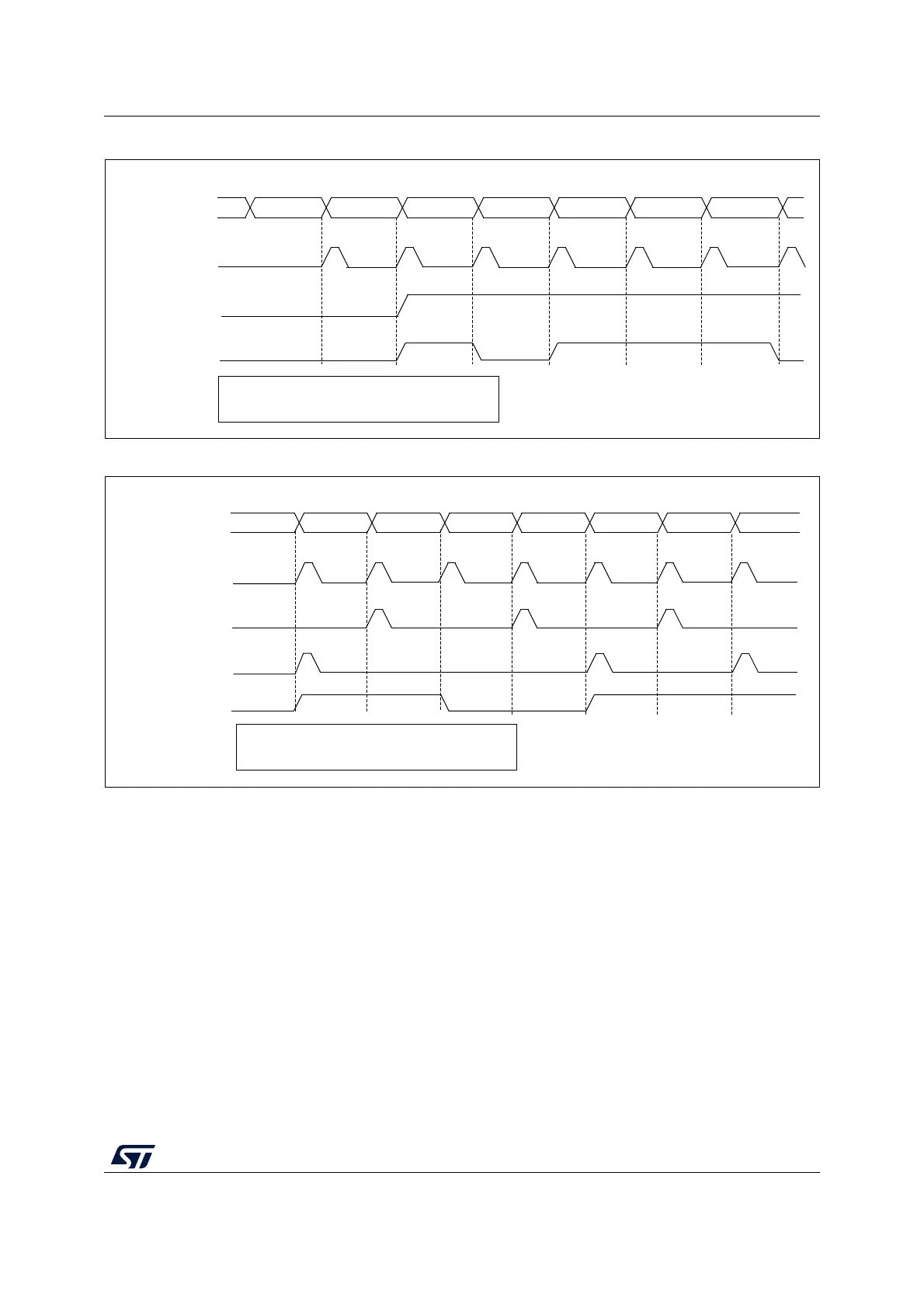

Figure 52. ADC1_AWD_OUT signal generation (on a single channel)

14.7.3 Analog watchdog threshold control

LT[11:0] and HT[11:0] can be changed during an analog-to-digital conversion (that is

between the start of the conversion and the end of conversion of the ADC internal state). If

LT and HT bits are programmed during the ADC guarded channel conversion, the watchdog

function is masked for this conversion. This mask is cleared when starting a new

conversion, and the resulting new AWD threshold is applied starting the next ADC

conversion result. AWD comparison is performed at each end of conversion. If the current

ADC data are out of the new threshold interval, this does not generated any interrupt or an

ADC_AWD1_OUT signal. The Interrupt and the ADC_AWD1_OUT generation only occurs

at the end of the ADC conversion that started after the threshold update. If

ADC_AWD1_OUT is already asserted, programming the new threshold does not deassert

the ADC_AWD1_OUT signal.

MSv65327V1

EOC FLAG

ADC STATE

RDY

AWD FLAG

Conversion1

outside

ADC_AWD1_OUT

inside

not cleared by SW

Conversion2 Conversion3 Conversion4 Conversion5 Conversion6 Conversion7

outsideinside outside outside inside

- Converted channels: 1,2,3,4,5,6,7

- Guarded converted channels: 1,2,3,4,5,6,7

MSv65328V1

EOC FLAG

ADC STATE

AWD FLAG

Conversion1

outside

ADCy_AWD1_OUT

Cleared

by SW

Conversion2 Conversion1 Conversion2 Conversion1 Conversion2 Conversion1

inside outside outside

Conversion2

EOS FLAG

Cleared

by SW

- Converted channels: 1 and 2

- Only channel 1 is guarded

Loading...

Loading...