RM0367 Rev 7 509/1043

RM0367 General-purpose timers (TIM2/TIM3)

546

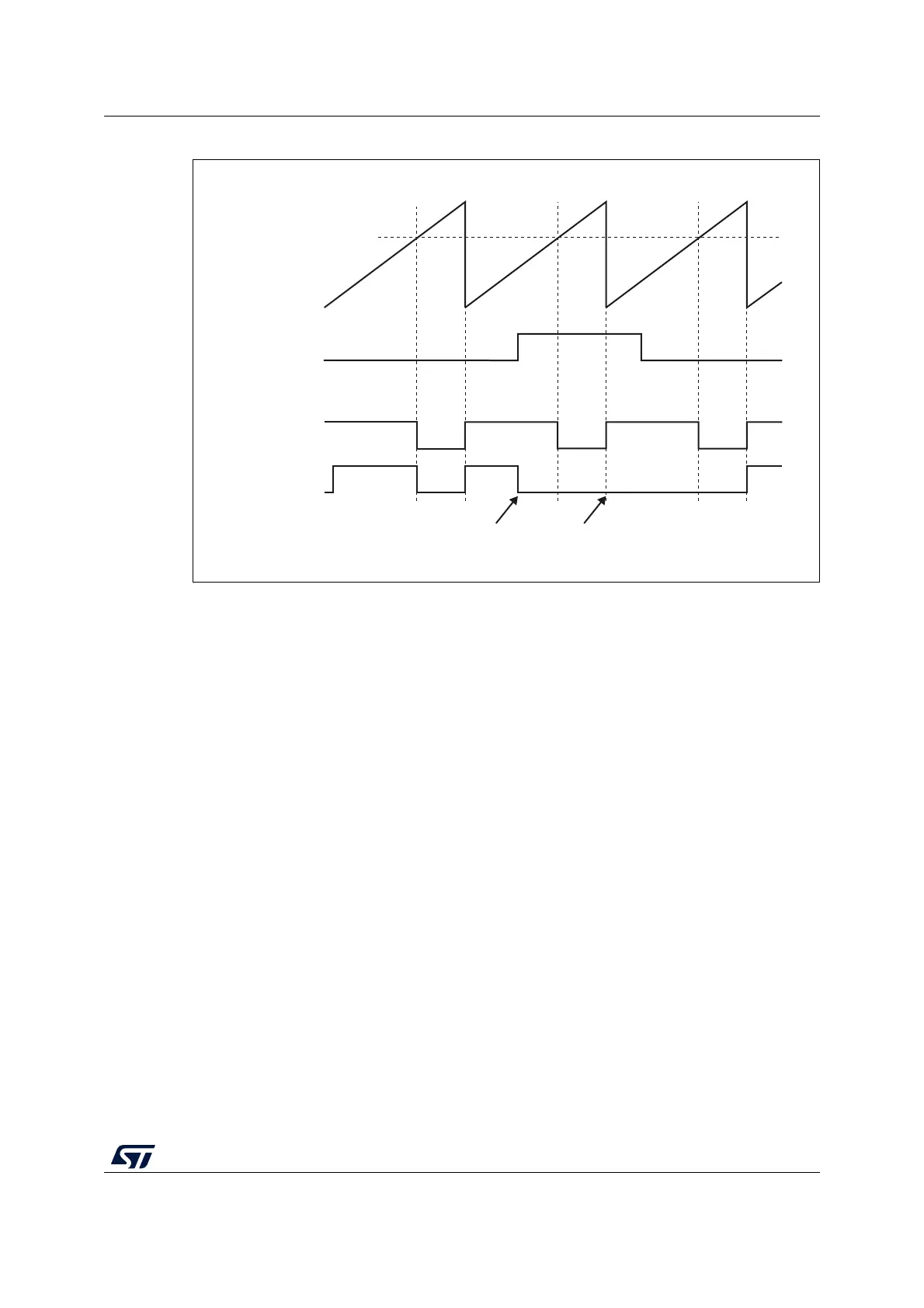

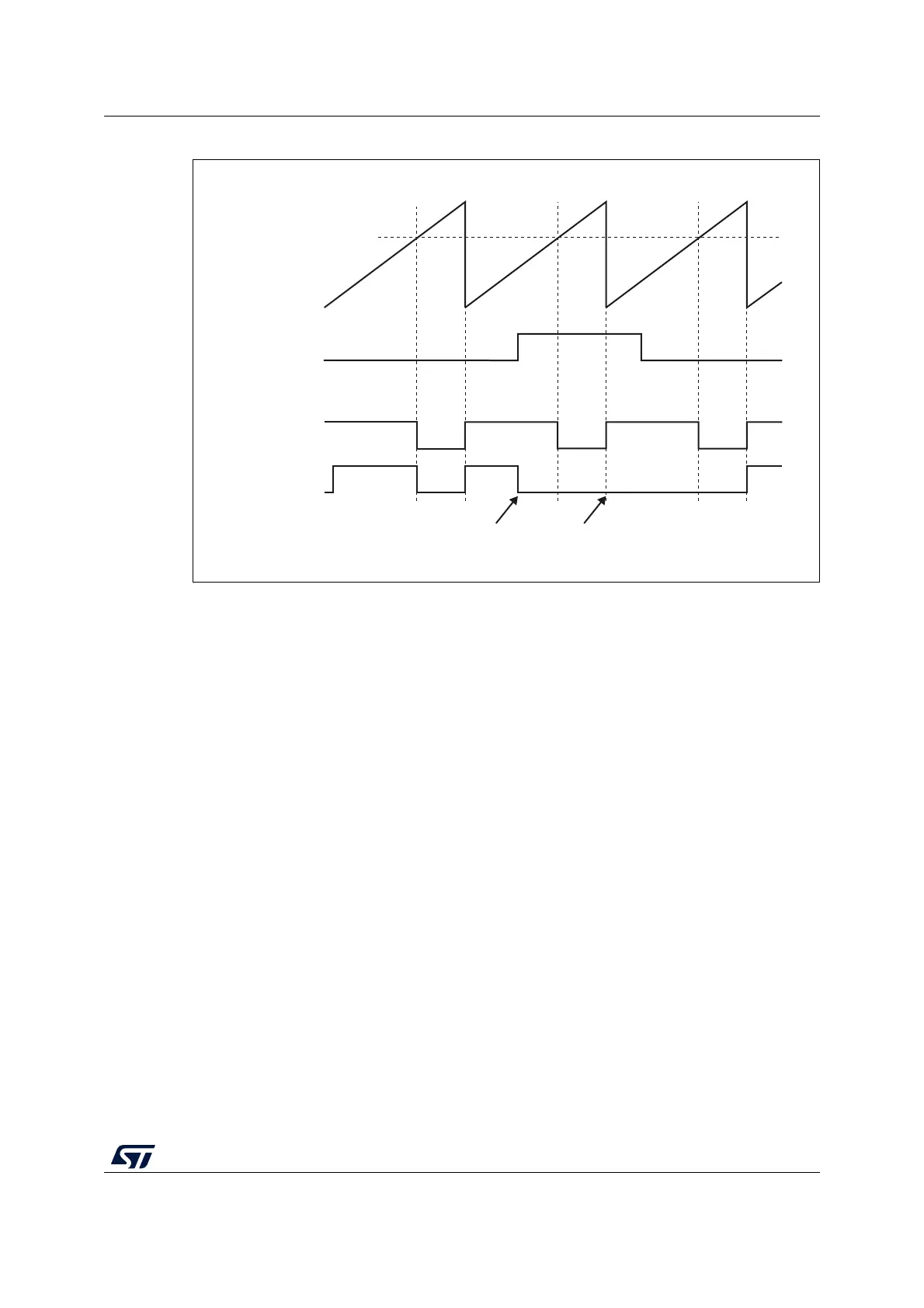

Figure 139. Clearing TIMx OCxREF

1. In case of a PWM with a 100% duty cycle (if CCRx>ARR), OCxREF is enabled again at the next counter

overflow.

21.3.12 Encoder interface mode

To select Encoder Interface mode write SMS=‘001 in the TIMx_SMCR register if the counter

is counting on TI2 edges only, SMS=010 if it is counting on TI1 edges only and SMS=011 if

it is counting on both TI1 and TI2 edges.

Select the TI1 and TI2 polarity by programming the CC1P and CC2P bits in the TIMx_CCER

register. CC1NP and CC2NP must be kept cleared. When needed, the input filter can be

programmed as well.

The two inputs TI1 and TI2 are used to interface to an incremental encoder. Refer to

Table 98. The counter is clocked by each valid transition on TI1FP1 or TI2FP2 (TI1 and TI2

after input filter and polarity selection, TI1FP1=TI1 if not filtered and not inverted,

TI2FP2=TI2 if not filtered and not inverted) assuming that it is enabled (CEN bit in

TIMx_CR1 register written to ‘1). The sequence of transitions of the two inputs is evaluated

and generates count pulses as well as the direction signal. Depending on the sequence the

counter counts up or down, the DIR bit in the TIMx_CR1 register is modified by hardware

accordingly. The DIR bit is calculated at each transition on any input (TI1 or TI2), whatever

the counter is counting on TI1 only, TI2 only or both TI1 and TI2.

Encoder interface mode acts simply as an external clock with direction selection. This

means that the counter just counts continuously between 0 and the auto-reload value in the

TIMx_ARR register (0 to ARR or ARR down to 0 depending on the direction). So the

TIMx_ARR must be configured before starting. In the same way, the capture, compare,

prescaler, trigger output features continue to work as normal.

In this mode, the counter is modified automatically following the speed and the direction of

the incremental encoder and its content, therefore, always represents the encoder’s

MS33105V1

(CCRx)

Counter (CNT)

ETRF

OCxREF

(OCxCE = ‘0’)

OCxREF

(OCxCE = ‘1’)

OCxREF_CLR

becomes high

OCxREF_CLR

still high

Loading...

Loading...