Inter-integrated circuit (I2C) interface RM0367

720/1043 RM0367 Rev 7

master re-launches automatically the slave address transmission until ACK is received. In

this case ADDRCF must be set if a NACK is received from the slave, in order to stop

sending the slave address.

If the I2C is addressed as a slave (ADDR=1) while the START bit is set, the I2C switches to

slave mode and the START bit is cleared, when the ADDRCF bit is set.

Note: The same procedure is applied for a Repeated Start condition. In this case BUSY=1.

Figure 226. Master initialization flowchart

For code example, refer to A.16.4: I2C configured in master mode to receive code example

andA.16.5: I2C configured in master mode to transmit code example.

Initialization of a master receiver addressing a 10-bit address slave

• If the slave address is in 10-bit format, the user can choose to send the complete read

sequence by clearing the HEAD10R bit in the I2C_CR2 register. In this case the master

automatically sends the following complete sequence after the START bit is set:

(Re)Start + Slave address 10-bit header Write + Slave address 2nd byte + REStart +

Slave address 10-bit header Read

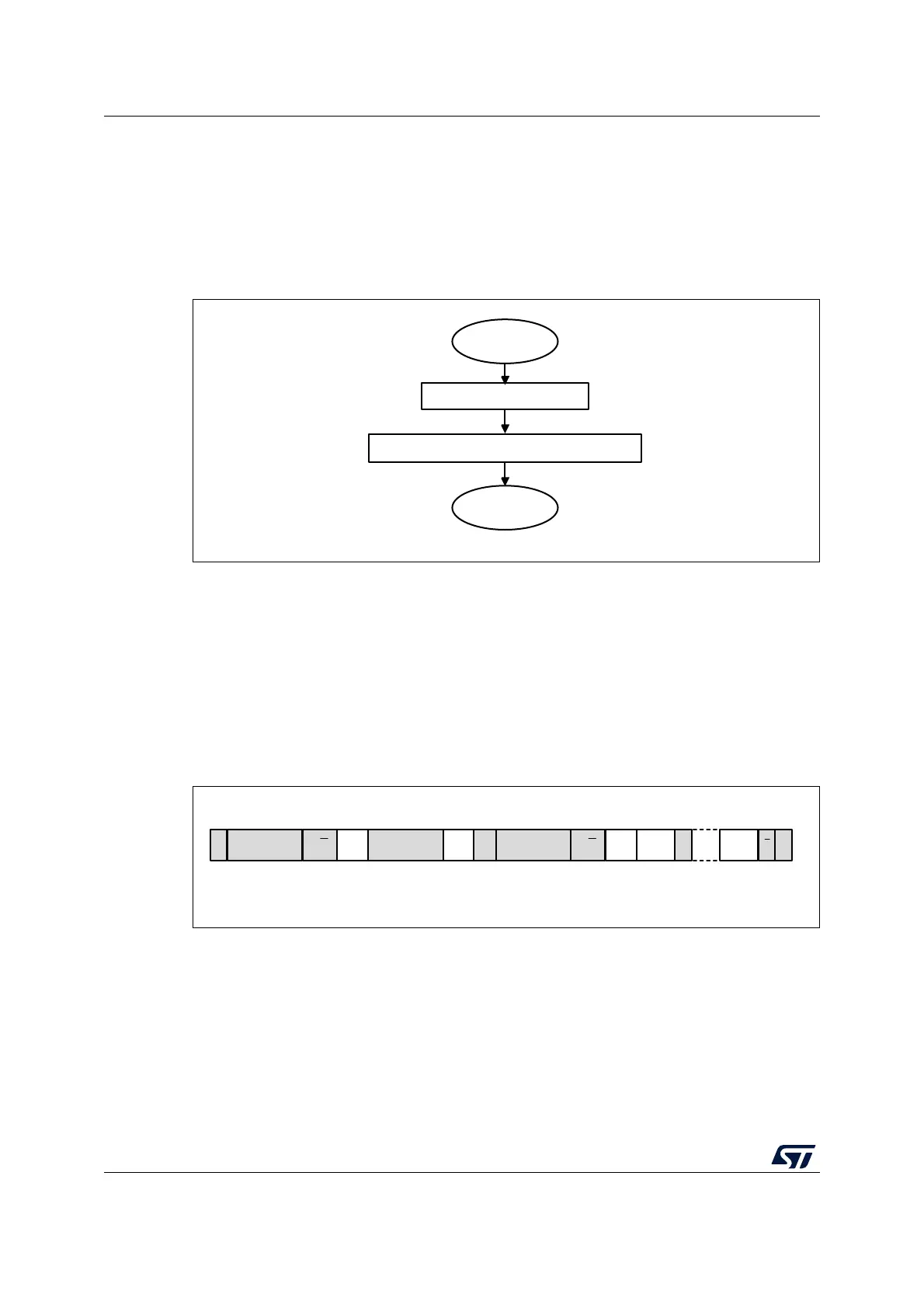

Figure 227. 10-bit address read access with HEAD10R=0

MS19859V2

Initial settings

Master

initialization

Enable interrupts and/or DMA in I2C_CR1

End

MSv41066V1

DATA A PADATA

Slave address

2nd byte

Slave address

1st 7 bits

SrA2A1 R/WR/W

Slave address

1st 7 bits

S A3

1 1 1 1 0 X X

1

1 1 1 1 0 X X

0

Write

Read

Loading...

Loading...