RM0367 Rev 7 681/1043

RM0367 Real-time clock (RTC)

694

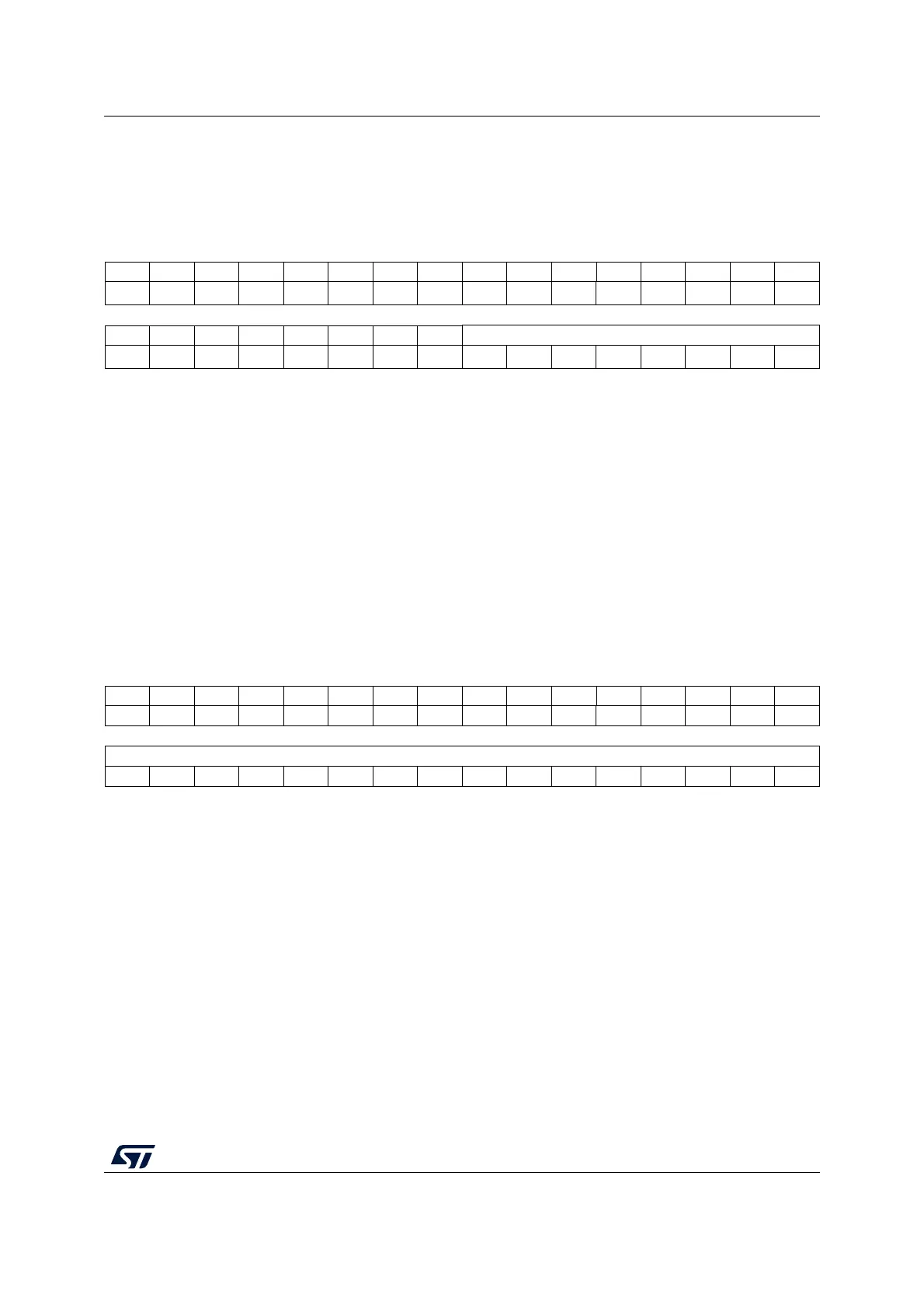

27.7.9 RTC write protection register (RTC_WPR)

Address offset: 0x24

Reset value: 0x0000 0000

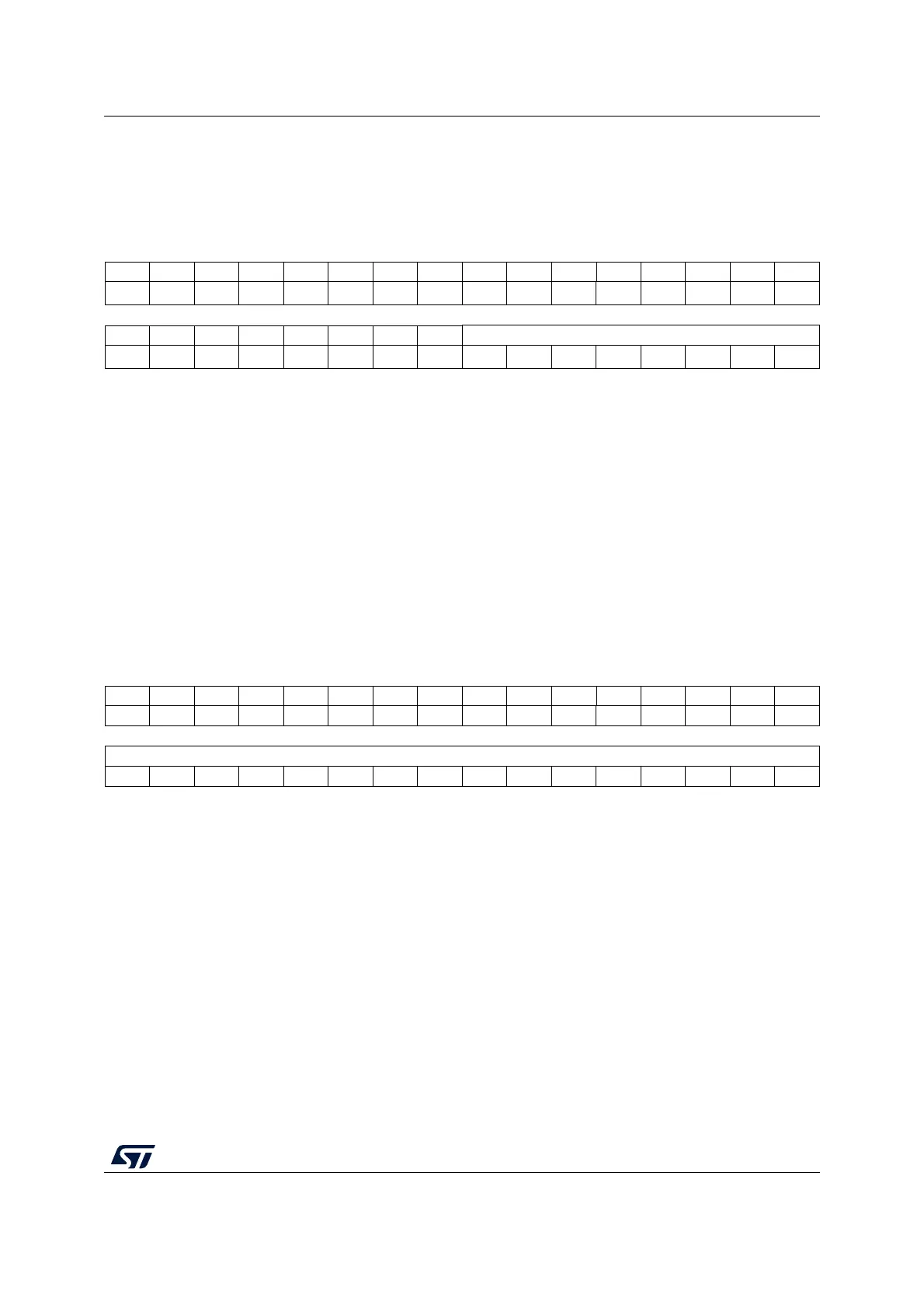

27.7.10 RTC sub second register (RTC_SSR)

Address offset: 0x28

RTC domain reset value: 0x0000 0000

System reset: 0x0000 0000 when BYPSHAD = 0. Not affected when BYPSHAD = 1.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. KEY[7:0]

wwwwwwww

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 KEY[7:0]: Write protection key

This byte is written by software.

Reading this byte always returns 0x00.

Refer to RTC register write protection for a description of how to unlock RTC register write

protection.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

SS[15:0]

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 SS[15:0]: Sub second value

SS[15:0] is the value in the synchronous prescaler counter. The fraction of a second is given by

the formula below:

Second fraction = (PREDIV_S - SS) / (PREDIV_S + 1)

Note: SS can be larger than PREDIV_S only after a shift operation. In that case, the correct

time/date is one second less than as indicated by RTC_TR/RTC_DR.

Loading...

Loading...