General-purpose timers (TIM2/TIM3) RM0367

544/1043 RM0367 Rev 7

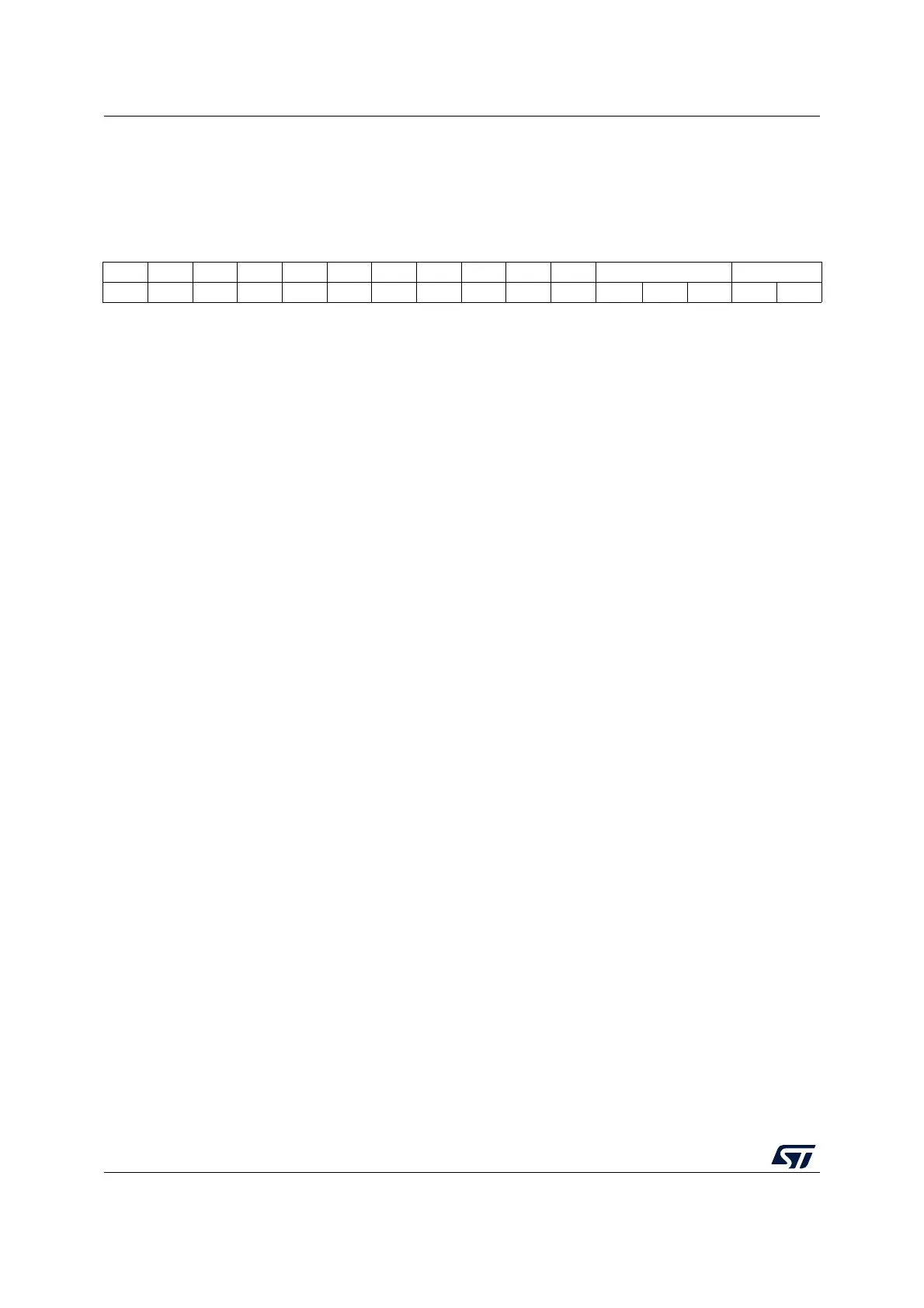

21.4.20 TIM3 option register (TIM3_OR)

Address offset: 0x50

Reset value: 0x0000

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TI_RMP ETR_RMP

rw rw rw rw rw

Bits 15:5 Reserved, must be kept at reset value.

Bit 4 TI_RMP: Timer3 remapping on PC9

This bit is set and cleared by software.

1: TIM3_CH4 selected

0: USB_NOE selected

Bit 3 TI_RMP: Timer3 remap on PB5

This bit is set and cleared by software.

1: TIM3_CH2 selected

0: TIM22_CH2 selected

Bit 2 TI_RMP: Timer3 TI remap

This bit is set and cleared by software.

1: TIM3_TI1 input is connected to PE3, PA6, PC6 or PB4

0: TIM3 _TI1 input is connected to USB_SOF

Bits 1:0 ETR_RMP: Timer3 ETR remap

These bits are set and cleared by software.

10: TIM3_ETR input is connected to HSI48 divided by 6 provided HSI48DIV6EN bit is set

(see Section 7.3.3: Clock recovery RC register (RCC_CRRCR))

others configurations: TIM3_ETR input is connected to PE2 or PD2

Loading...

Loading...