Debug support (DBG) RM0367

956/1043 RM0367 Rev 7

33 Debug support (DBG)

33.1 Overview

The STM32L0x3 devices are built around a Cortex

®

-M0+ core which contains hardware

extensions for advanced debugging features. The debug extensions allow the core to be

stopped either on a given instruction fetch (breakpoint) or data access (watchpoint). When

stopped, the core’s internal state and the system’s external state may be examined. Once

examination is complete, the core and the system may be restored and program execution

resumed.

The debug features are used by the debugger host when connecting to and debugging the

STM32L0x3 MCUs.

One interface for debug is available:

• Serial wire

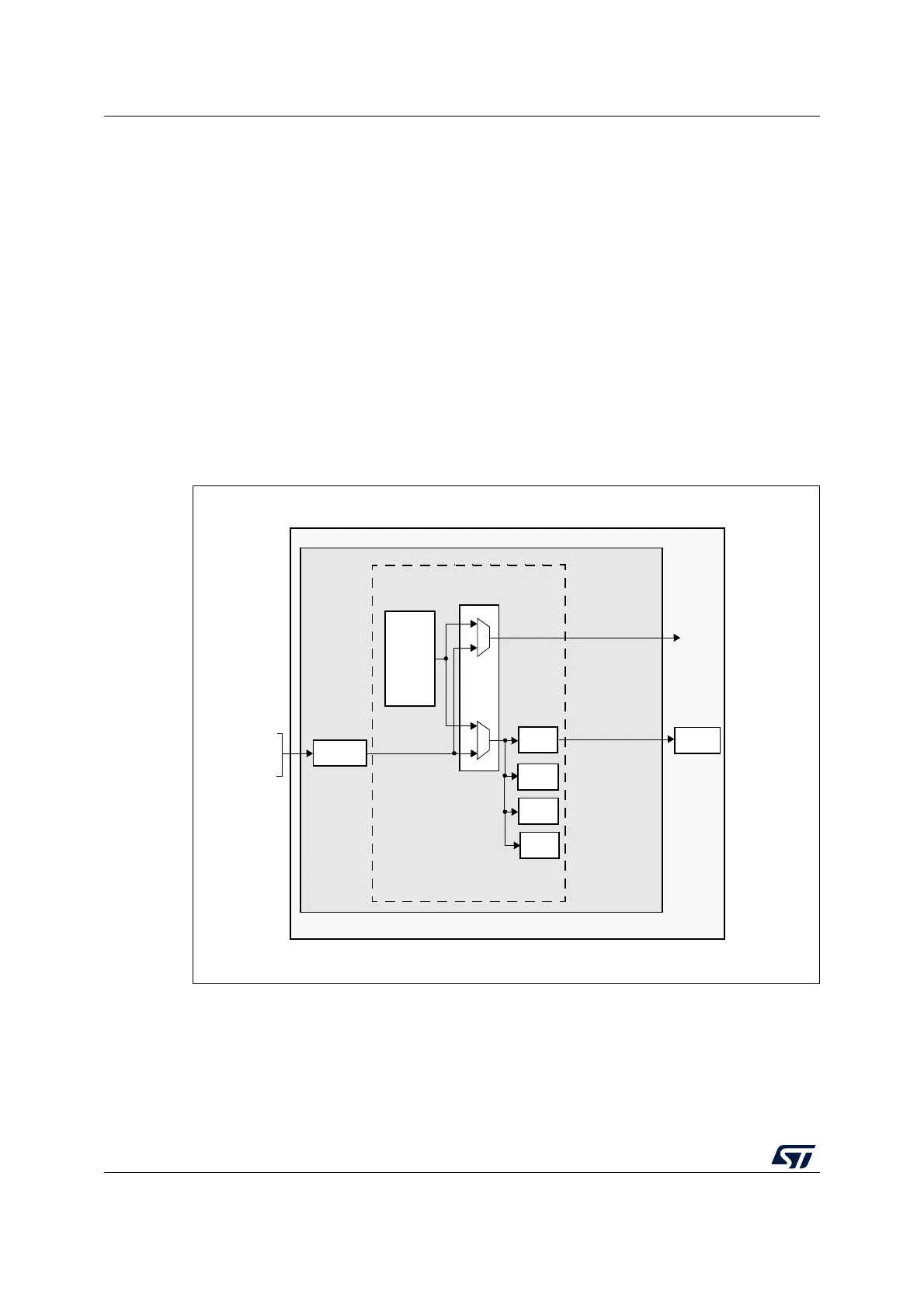

Figure 315. Block diagram of STM32L0x3 MCU and Cortex

®

-M0+-level debug support

1. The debug features embedded in the Cortex

®

-M0+ core are a subset of the Arm

®

CoreSight Design Kit.

The Arm

®

Cortex

®

-M0+ core provides integrated on-chip debug support. It is comprised of:

• SW-DP: Serial wire

• BPU: Break point unit

• DWT: Data watchpoint trigger

Cortex-M0

Core

SW-DP

Bridge

NVIC

DWT

BPU

System

interface

Debug AP

Bus matrix

DBGMCU

STM32 MCU debug suppo rt

Cortex-M0 debug support

SWDIO

SWCLK

MS19240V2

Debug AP

Loading...

Loading...