AES hardware accelerator (AES) RM0367

446/1043 RM0367 Rev 7

ECB/CBC encryption sequence

The sequence of events to perform an ECB/CBC encryption (more detail in Section 19.4.4):

1. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

2. Select the Mode 1 by to 00 the MODE[1:0] bitfield of the AES_CR register and select

ECB or CBC chaining mode by setting the CHMOD[1:0] bitfield of the AES_CR register

to 00 or 01, respectively. Data type can also be defined, using DATATYPE[1:0] bitfield.

3. Write the AES_KEYRx registers (128 bits) with encryption key. Fill the AES_IVRx

registers with the initialization vector data if CBC mode has been selected.

4. Enable the AES peripheral by setting the EN bit of the AES_CR register.

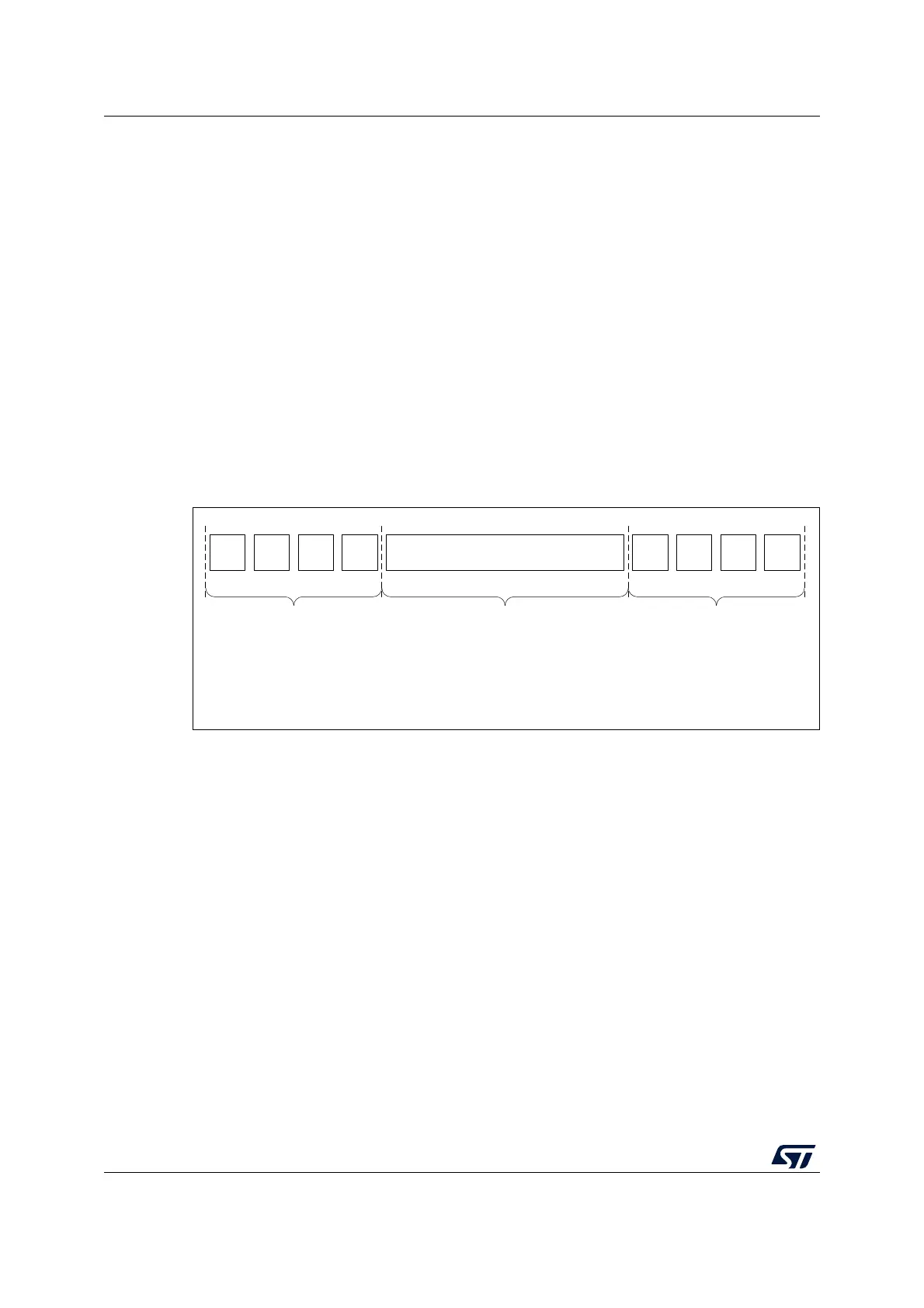

5. Write the AES_DINR register four times to input the plaintext (MSB first), as shown in

Figure 95.

6. Wait until the CCF flag is set in the AES_SR register.

7. Read the AES_DOUTR register four times to get the ciphertext (MSB first) as shown in

Figure 95. Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

8. Repeat steps 5,6,7to process all the blocks with the same encryption key.

Figure 95. ECB/CBC encryption (Mode 1)

ECB/CBC decryption sequence

The sequence of events to perform an AES ECB/CBC decryption is as follows (more detail

in Section 19.4.4):

1. Follow the steps described in Section 19.4.5: AES decryption key preparation on

page 441, in order to prepare the decryption key in AES core.

2. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

3. Select the Mode 3 by setting to 10 the MODE[1:0] bitfield of the AES_CR register and

select ECB or CBC chaining mode by setting the CHMOD[1:0] bitfield of the AES_CR

register to 00 or 01, respectively. Data type can also be defined, using DATATYPE[1:0]

bitfield.

4. Write the AES_IVRx registers with the initialization vector (required in CBC mode only).

5. Enable AES by setting the EN bit of the AES_CR register.

6. Write the AES_DINR register four times to input the cipher text (MSB first), as shown in

Figure 96.

7. Wait until the CCF flag is set in the AES_SR register.

8. Read the AES_DOUTR register four times to get the plain text (MSB first), as shown in

Figure 96. Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

MS18936V3

WR

PT3

WR

PT2

WR

PT1

WR

PT0

Wait until flag CCF = 1

RD

CT3

RD

CT2

RD

CT1

RD

CT0

Input phase

4 write operations into

AES_DINR[31:0]

Computation phase

Output phase

4 read operations of

AES_DOUTR[31:0]

PT = plaintext = 4 words (PT3, … , PT0)

CT = ciphertext = 4 words (CT3, … , CT0)

MSB LSB MSB LSB

Loading...

Loading...